intel Penyusun Sintesis Tahap Tinggi Edisi Pro

Maklumat Produk

| Nama Produk | Intel High-Level Synthesis Compiler Edisi Pro |

|---|---|

| Versi | 22.4 |

| Tarikh Tayangan | 19 Disember 2022 |

| Notis Penamatan | Pengkompil Sintesis Tahap Tinggi Intel dirancang untuk menjadi ditamatkan selepas Versi 23.4. |

Arahan Penggunaan Produk

Panduan Bermula

- Mulakan persekitaran pengkompil anda.

- Review pelbagai reka bentuk examppelajaran dan tutorial disediakan dengan Pengkompil Intel HLS.

Panduan Pengguna

- Panduan Pengguna menyediakan arahan tentang

- Mensintesis, mengesahkan dan mensimulasikan harta intelek (IP) yang direka untuk produk Intel FPGA.

- Menerusi keseluruhan aliran pembangunan komponen anda daripada mencipta komponen dan meja ujian anda sehingga menyepadukan IP komponen anda ke dalam sistem yang lebih besar dengan perisian Intel Quartus Prime.

Panduan Amalan Terbaik

Panduan Amalan Terbaik menyediakan teknik dan amalan yang boleh anda gunakan untuk meningkatkan penggunaan kawasan FPGA dan prestasi komponen HLS anda. Gunakan amalan terbaik ini selepas mengesahkan ketepatan fungsi komponen anda.

Manual Rujukan

Manual Rujukan menyediakan maklumat rujukan tentang ciri yang disokong oleh Pengkompil Intel HLS. Cari butiran tentang pilihan arahan Pengkompil Intel HLS, pengepala files, pragma, atribut, makro, pengisytiharan, hujah dan pustaka templat.

Nota Keluaran Intel® High Level Synthesis Compiler Pro Edition Versi 22.4

- Nota Keluaran Intel® High Level Synthesis Compiler Pro Edition memberikan maklumat terkini tentang Intel High Level Synthesis Compiler Pro Edition Versi 22.4.

Menamatkan Penamatan Intel HLS Compiler

- Untuk mengekalkan akses kepada ciri reka bentuk peringkat tinggi FPGA terkini, pengoptimuman dan utiliti pembangunan, pindahkan reka bentuk sedia ada anda untuk menggunakan Kit Alat Pangkalan Intel oneAPI.

- Pengkompil Intel High Level Synthesis (HLS) dirancang untuk ditamatkan selepas Versi 23.4.

- Lawati halaman produk Intel oneAPI untuk nasihat migrasi, atau pergi ke forum komuniti Reka Bentuk Tahap Tinggi Intel untuk sebarang pertanyaan atau permintaan.

Mengenai Perpustakaan Dokumentasi Edisi Intel HLS Compiler Pro

- Dokumentasi untuk Intel HLS Compiler Pro Edition dibahagikan kepada beberapa penerbitan. Gunakan jadual berikut untuk mencari penerbitan yang mengandungi maklumat Intel HLS Compiler Pro Edition yang anda cari:

Jadual 1. Perpustakaan Dokumentasi Edisi Pro Pengkompil Sintesis Tahap Tinggi Intel

| Tajuk dan Penerangan | |

| Nota Keluaran

Menyediakan maklumat terkini tentang Pengkompil Intel HLS. |

Pautan |

| Panduan Bermula

Bangun dan jalankan dengan Intel HLS Compiler dengan mempelajari cara untuk memulakan persekitaran pengkompil anda dan semulaviewdalam pelbagai reka bentuk examppelajaran dan tutorial disediakan dengan Pengkompil Intel HLS. |

Pautan |

| Panduan Pengguna

Menyediakan arahan tentang mensintesis, mengesahkan dan mensimulasikan harta intelek (IP) yang anda reka bentuk untuk produk Intel FPGA. Ikuti keseluruhan aliran pembangunan komponen anda daripada mencipta komponen dan testbench anda sehingga menyepadukan IP komponen anda ke dalam sistem yang lebih besar dengan perisian Intel Quartus Prime. |

Pautan |

| Panduan Amalan Terbaik

Menyediakan teknik dan amalan yang boleh anda gunakan untuk meningkatkan penggunaan kawasan FPGA dan prestasi komponen HLS anda. Biasanya, anda menggunakan amalan terbaik ini selepas anda mengesahkan ketepatan fungsi komponen anda. |

Pautan |

| Manual Rujukan

Menyediakan maklumat rujukan tentang ciri yang disokong oleh Pengkompil Intel HLS. Cari butiran tentang pilihan arahan Pengkompil Intel HLS, pengepala files, pragma, atribut, makro, pengisytiharan, hujah dan pustaka templat. |

Pautan |

Perbadanan Intel. Hak cipta terpelihara. Intel, logo Intel dan tanda Intel lain ialah tanda dagangan Intel Corporation atau anak syarikatnya. Intel menjamin prestasi produk FPGA dan semikonduktornya mengikut spesifikasi semasa menurut waranti standard Intel, tetapi berhak untuk membuat perubahan pada mana-mana produk dan perkhidmatan pada bila-bila masa tanpa notis. Intel tidak memikul tanggungjawab atau liabiliti yang timbul daripada aplikasi atau penggunaan mana-mana maklumat, produk atau perkhidmatan yang diterangkan di sini kecuali seperti yang dipersetujui secara bertulis oleh Intel. Pelanggan Intel dinasihatkan untuk mendapatkan versi terkini spesifikasi peranti sebelum bergantung pada sebarang maklumat yang diterbitkan dan sebelum membuat pesanan untuk produk atau perkhidmatan.

*Nama dan jenama lain boleh dituntut sebagai hak milik orang lain.

Menamatkan Penamatan Intel HLS Compiler

- Untuk mengekalkan akses kepada ciri reka bentuk peringkat tinggi FPGA terkini, pengoptimuman dan utiliti pembangunan, pindahkan reka bentuk sedia ada anda untuk menggunakan Kit Alat Pangkalan Intel oneAPI.

- Pengkompil Intel High Level Synthesis (HLS) dirancang untuk ditamatkan selepas Versi 23.4.

- Lawati halaman produk Intel oneAPI untuk nasihat migrasi, atau pergi ke forum komuniti Reka Bentuk Tahap Tinggi Intel untuk sebarang pertanyaan atau permintaan.

Ciri dan Penambahbaikan Baharu

- Intel High Level Synthesis Compiler Pro Edition Versi 22.4 termasuk ciri baharu berikut:

- Pelepasan penyelenggaraan.

- Tiada ciri atau peningkatan baharu untuk Intel HLS Compiler Pro Edition Versi 22.4.

Perubahan dalam Gelagat Perisian

- Bahagian ini mendokumenkan keadaan di mana ciri Intel HLS Compiler Pro Edition Versi 22.4 telah berubah daripada keluaran terdahulu pengkompil.

Pelepasan penyelenggaraan.

- Tiada perubahan dalam tingkah laku perisian untuk Intel HLS Compiler Pro Edition Version 22.4.

Prasyarat Intel High-Level Synthesis Compiler Edisi Pro

- Intel HLS Compiler Pro Edition ialah sebahagian daripada Suite Reka Bentuk Edisi Perdana Intel Quartus® Prime Pro. Anda boleh memasang Intel HLS Compiler sebagai sebahagian daripada pemasangan perisian Intel Quartus Prime anda atau memasangnya secara berasingan. Ia memerlukan Intel Quartus Prime dan perisian tambahan untuk digunakan.

- Untuk arahan terperinci tentang memasang perisian Intel Quartus Prime Pro Edition, termasuk keperluan sistem, prasyarat dan keperluan pelesenan, lihat Pemasangan dan Pelesenan Perisian Intel FPGA.

- Pengkompil Intel HLS memerlukan perisian berikut sebagai tambahan kepada Intel Quartus Prime:

Penyusun C ++

- Di Linux, Intel HLS Compiler memerlukan GCC 9.3.0 termasuk perpustakaan GNU C++ dan utiliti binari (binutils).

- Versi GCC ini disediakan sebagai sebahagian daripada pemasangan Intel HLS Compiler anda. Selepas memasang Intel HLS Compiler, GCC 9.3.0 tersedia dalam /gcc.

- Penting: Pengkompil Intel HLS menggunakan /gcc sebagai direktori rantai alatnya. Gunakan pemasangan GCC ini untuk semua kerja reka bentuk berkaitan HLS anda.

- Untuk Windows, pasang salah satu daripada versi Microsoft* Visual Studio* Professional berikut:

- Microsoft Visual Studio 2017 Professional

- Komuniti Microsoft Visual Studio 2017

- Untuk sokongan C++17 yang paling terkini, pastikan anda menggunakan versi terkini Visual Studio 2017.

- Penting: Perisian Intel HLS Compiler tidak menyokong versi Microsoft Visual Studio selain daripada yang ditentukan untuk edisi perisian.

Siemens* Perisian Simulasi EDA Questa®

- Pada sistem Windows dan RedHat Linux, anda boleh memasang perisian simulasi Questa® daripada pemasang perisian Intel Quartus Prime. Pilihan yang tersedia adalah seperti berikut:

- Questa Intel FPGA Edition

- Questa Intel FPGA Edisi Permulaan

- Kedua-dua Questa Intel FPGA Edition dan Questa Intel FPGA Starter Edition memerlukan lesen. Lesen untuk Questa Intel FPGA Starter Edition adalah percuma. Untuk butiran, rujuk Pemasangan dan Pelesenan Perisian Intel FPGA.

- Sebagai alternatif, anda boleh menggunakan versi berlesen anda sendiri bagi perisian Siemens* EDA ModelSim* SE atau Siemens EDA Questa Advanced Simulator.

- Pada sistem Linux, Questa – Intel FPGA Edition dan Questa – Intel FPGA Starter Edition memerlukan pakej alat pembangunan Red Hat*.

- Untuk maklumat tentang semua versi perisian ModelSim dan Questa yang disokong oleh perisian Intel, rujuk bahagian Maklumat Antara Muka EDA dalam Nota Keluaran Sokongan Perisian dan Peranti untuk edisi Intel Quartus Prime Pro Edition anda.

Maklumat Berkaitan

- Panduan Permulaan Pengkompil Sintesis Tahap Tinggi Intel

- Sistem Operasi yang Disokong

- Keperluan Perisian dalam Pemasangan dan Pelesenan Perisian Intel FPGA

- Maklumat Antara Muka EDA (Edisi Intel Quartus Prime Pro)

Isu Diketahui dan Penyelesaian

- Bahagian ini menyediakan maklumat tentang isu yang diketahui yang mempengaruhi Intel HLS Compiler Pro Edition Versi 22.4.

| Penerangan | Penyelesaian |

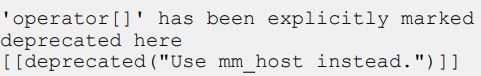

| Apabila anda menggunakan kelas mm_master yang tidak digunakan, pengkompil mengeluarkan mesej amaran seperti berikut:

Mesej ini tidak menunjukkan bahagian kod anda yang perlu diubah. |

Elakkan mesej amaran ini dengan menggunakan kelas mm_host, yang menggantikan kelas mm_master yang tidak digunakan lagi. |

| (Windows sahaja) Menyusun reka bentuk dalam direktori dengan nama laluan yang panjang boleh mengakibatkan kegagalan penyusunan.

Semak debug.log file kerana “tidak dapat mencari file” kesilapan. Ralat ini boleh menunjukkan bahawa laluan anda terlalu panjang. |

Susun reka bentuk dalam direktori dengan nama laluan pendek. |

| (Windows sahaja) Laluan panjang untuk direktori pemasangan Intel Quartus Prime anda boleh menghalang anda daripada berjaya menyusun dan menjalankan tutorial dan bekas Intel HLS Compilerampreka bentuk le.

Semak debug.log file kerana “tidak dapat mencari file” kesilapan. Ralat ini boleh menunjukkan bahawa laluan anda terlalu panjang. |

Pindahkan tutorial dan bekasamples kepada nama laluan pendek sebelum cuba menjalankannya. |

| Penerangan | Penyelesaian |

| Perpustakaan yang menyasarkan OpenCL* dan ditulis dalam HLS tidak boleh menggunakan strim atau paip sebagai antara muka antara kod OpenCL dan pustaka yang ditulis dalam HLS.

Walau bagaimanapun, perpustakaan dalam HLS boleh menggunakan aliran atau paip jika kedua-dua titik akhir berada dalam pustaka (contohnyaample, aliran yang menghubungkan dua fungsi tugas). |

T/A |

| Menggunakan parameter ihc::maxburst pada antara muka hos yang Dipetakan Memori Avalon® boleh menyebabkan reka bentuk anda tergantung dalam simulasi. | T/A |

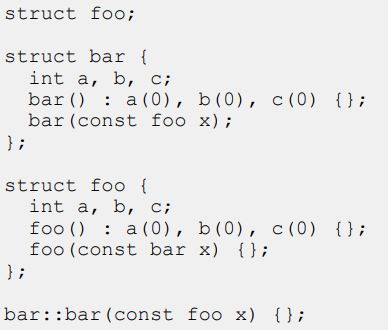

| Dalam beberapa kes yang tidak biasa, jika anda mempunyai dua kelas yang mana setiap pembinanya memerlukan contoh kelas lain sebagai input, pengkompil mungkin ranap.

Untuk example, menyusun coretan kod berikut menyebabkan pengkompil ranap:

|

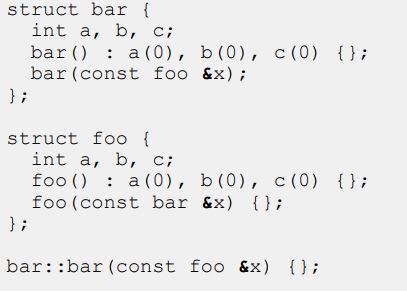

Elakkan membuat definisi bulat. Sebaliknya, gunakan penunjuk atau rujukan dalam pembina salinan anda.

Untuk example, ubah coretan kod terdahulu ke dalam kod berikut dan masukkan struct sebagai rujukan kepada pembina:

|

| Perpustakaan yang menyasarkan OpenCL dan ditulis dalam HLS mungkin menyebabkan kernel OpenCL yang termasuk perpustakaan mempunyai kompilasi tambahan yang lebih konservatif. | T/A |

| Apabila membangunkan perpustakaan, jika anda mempunyai #define mentakrifkan nilai yang anda gunakan kemudian dalam #pragma, arahan fpga_crossgen gagal.

Untuk example, kod berikut tidak boleh disusun oleh

|

Gunakan pragma dan bukannya #pragma.

Untuk example, yang berikut berjaya disusun dengan

|

| Apabila anda menggunakan pilihan arahan -c untuk mempunyai kompilasi dan pemautan yang berasingan stages dalam aliran kerja anda, dan jika anda tidak menentukan pilihan -march dalam pautan stage (atau nyatakan nilai pilihan -march yang berbeza), pemautan anda stage mungkin gagal dengan atau tanpa mesej ralat. | Pastikan anda menggunakan nilai pilihan -march yang sama untuk kedua-dua kompilasi dengan pilihan arahan -c stage dan penghubung stage. |

| Penerangan | Penyelesaian |

| Menggunakan atribut memori hls_merge pada tatasusunan yang diisytiharkan dalam gelung yang dibuka atau sebahagiannya dibuka menyebabkan salinan tatasusunan digabungkan merentasi lelaran gelung yang dibuka.

|

Elakkan daripada menggunakan atribut memori hls_merge dalam gelung yang dibuka.

Jika anda perlu menggabungkan kenangan dalam gelung yang dibuka, isytiharkan tatasusunan jenis struct secara eksplisit untuk penggabungan lebar, atau isytiharkan tatasusunan yang lebih dalam untuk penggabungan kedalaman.

|

| Dalam Memori Fungsi Viewer laporan reka bentuk peringkat tinggi, beberapa ingatan skop fungsi mungkin muncul sebagai "dioptimumkan". | tiada.

Apabila a file mengandungi fungsi yang merupakan komponen dan fungsi yang bukan komponen, semua pembolehubah berskop fungsi disenaraikan dalam anak tetingkap Senarai Memori Fungsi, tetapi hanya pembolehubah daripada komponen mempunyai maklumat tentangnya untuk ditunjukkan dalam Memori Fungsi View anak tetingkap. |

| Beberapa laporan reka bentuk peringkat tinggi gagal dalam Microsoft Internet Explorer*. | Gunakan salah satu daripada pelayar berikut untuk view laporan:

• Google Chrome* • Microsoft Edge* • Mozilla Firefox* |

| Gelung Viewer dalam Laporan Reka Bentuk Peringkat Tinggi mempunyai sekatan berikut:

• Tingkah laku kelompok bebas gerai tidak dimodelkan dalam Gelung Vieweh. Kependaman akhir ditunjukkan dalam Gelung Viewer untuk kluster bebas gerai biasanya lebih pesimis (iaitu, lebih tinggi) daripada kependaman sebenar reka bentuk anda. Untuk penerangan tentang kluster dan kluster bebas gerai, rujuk Mengelompokkan Datapath dalam Intel Tahap Tinggi Panduan Amalan Terbaik Synthesis Compiler Edisi Pro. • Gerai daripada baca dan tulis daripada ingatan atau kenyataan cetakan tidak dimodelkan. • Kiraan lelaran tinggi (>1000) menyebabkan prestasi Gelung yang perlahan Vieweh. • Anda tidak boleh menentukan kiraan lelaran sifar (0) dalam Gelung Vieweh. |

tiada. |

| Pautan dalam beberapa laporan dalam Laporan Reka Bentuk Tahap Tinggi yang dijana pada sistem Windows tidak berfungsi. | Hasilkan Laporan Reka Bentuk Tahap Tinggi (iaitu, susun kod anda) pada sistem Linux. |

| Menggunakan struct jenis data ac_int tunggal dalam antara muka mengukus yang menggunakan paket (ihc::usesPackets ) tidak berfungsi.

Untuk example, coretan kod berikut tidak berfungsi:

|

Untuk menggunakan gabungan ini dalam reka bentuk anda, patuhi sekatan berikut:

• Saiz data ac_int dalaman mestilah berbilang 8 • Pengisytiharan jenis antara muka strim mesti dinyatakan ihc::bitsPerSymbol<8> Untuk example, coretan kod berikut berfungsi:

|

| Penerangan | Penyelesaian | |

| Apabila menjalankan simulasi pemprosesan tinggi komponen anda menggunakan panggilan fungsi enqueue, jika anda tidak menggunakan fungsi ihc_hls_component_run_all untuk menjalankan panggilan komponen yang dienqueue selepas semua panggilan ihc_hls_enqueue untuk komponen itu, gelagat berikut berlaku:

• Dalam emulasi, fungsi komponen enqueued dijalankan. • Dalam simulasi, fungsi komponen beratur tidak dijalankan, tanpa ralat atau mesej amaran disediakan. |

Pastikan anda menggunakan fungsi ihc_hls_component_run_all selepas semua ihc_hls_enqueue memanggil komponen tersebut untuk menjalankan panggilan fungsi komponen yang beratur. | |

| Melancarkan fungsi tugas dengan ihc::launch_always_run | Untuk mengelakkan pelucutan pengoptimuman, tambahkan seketika(1) | |

| menanggalkan atribut pengoptimuman yang digunakan pada tugas | gelung pada fungsi terjejas gunakan kawalan yang sepadan | |

| fungsi. | pragma kepada gelung while(1) dan bukannya fungsi. | |

| Dalam kod berikut example, atribut yang digunakan pada fungsi diabaikan. Laporan Reka Bentuk Tahap Tinggi menunjukkan II daripada 1 untuk tugasan ini dan bukannya II daripada 4 yang diminta. | Contoh kod berikutampsaya tunjukkan bagaimana anda boleh melaksanakan perubahan ini untuk kod yang terdahulu example: | |

|

|

|

| Untuk projek Cyclone® V yang mengandungi berbilang komponen HLS, apabila anda menggunakan perintah i++ untuk menyusun projek anda kepada perkakasan (i++ -march=CycloneV), anda mungkin menerima ralat.

Walaupun teks ralat berbeza bergantung pada projek anda, tandatangan ralat adalah kegagalan kompilasi Intel Quartus Prime disebabkan sintaks Verilog yang buruk. Modul cuba menggunakan fungsi yang tidak dapat ditemui oleh pengkompil Intel Quartus Prime. |

Jika anda menghadapi masalah ini, letakkan setiap komponen HLS dalam projek yang berasingan. | |

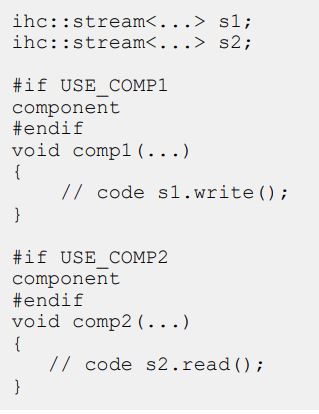

| Menyusun beberapa reka bentuk yang mengandungi berbilang komponen menjana ralat tentang penggunaan semula strim. | Jika anda menghadapi masalah ini, susun setiap komponen dalam reka bentuk secara berasingan. Anda mungkin perlu menambah makro pada kod anda untuk membolehkan setiap komponen disusun secara berasingan. | |

| Pertimbangkan contoh berikutample: | ||

|

||

Arkib Nota Keluaran Intel High-Level Synthesis Compiler Pro Edition

Untuk versi terkini dan sebelumnya bagi panduan pengguna ini, rujuk Nota Keluaran Intel HLS Compiler Pro Edition. Jika versi perisian tidak disenaraikan, nota keluaran untuk versi perisian sebelumnya digunakan.

Sejarah Semakan Dokumen untuk Nota Keluaran Intel HLS Compiler Pro Edition Versi 22.4

| Versi Dokumen | Versi Intel Quartus Prime | Perubahan |

| 2022.12.19 | 22.4 | • Keluaran awal. |

Dokumen / Sumber

|

Intel High Level Synthesis Compiler Edisi Pro [pdf] Arahan Versi 22.4, Versi 23.4, Edisi Pro Pengkompil Sintesis Tahap Tinggi, Pengkompil Sintesis Tahap Tinggi, Edisi Pro |