Blok Tatasusunan Logik Agilex intel dan Modul Logik Adaptif

Intel® Agilex™ LAB dan ALM Overview

Blok tatasusunan logik (LAB) terdiri daripada blok binaan asas yang dikenali sebagai modul logik penyesuaian (ALM). Anda boleh mengkonfigurasi LAB untuk melaksanakan fungsi logik, fungsi aritmetik dan fungsi daftar.

Anda boleh menggunakan separuh daripada LAB yang tersedia dalam peranti Intel® Agilex™ sebagai LAB memori (MLAB). Peranti tertentu mungkin mempunyai nisbah MLAB yang lebih tinggi.

Perisian Intel Quartus® Prime dan alatan sintesis pihak ketiga yang disokong secara automatik memilih mod yang sesuai untuk fungsi biasa seperti pembilang, penambah, penolakan dan fungsi aritmetik.

Seni Bina Teras Intel Hyperflex™, Peranti Intel Agilex Overview

Menyediakan maklumat lanjut tentang Hyper-Registers dan seni bina teras Intel Hyperflex™. Hyper-Register ialah daftar tambahan yang tersedia dalam setiap segmen penghalaan antara sambungan di seluruh fabrik teras, termasuk segmen penghalaan yang disambungkan kepada input dan output LAB.

Daftar Intel Hyperflex™

Keluarga peranti Intel Agilex adalah berdasarkan seni bina teras Intel Hyperflex™.

Intel Agilex LAB mengandungi daftar Intel Hyperflex dan ciri-ciri lain yang direka untuk memudahkan penamatan semula. Daftar Intel Hyperflex tersedia dalam ALM dan rantai pembawa. Seperti yang ditunjukkan dalam angka Butiran Sambungan Intel Agilex ALM, daftar Intel Hyperflex terletak pada jelas segerak dan jam membolehkan input menambah atau mengurangkan kelewatan laluan. Semua daftar Intel Hyperflex boleh didayakan dan dikawal oleh perisian Intel Quartus Prime semasa penamatan.

Seni Bina dan Ciri Intel Agilex LAB dan ALM

Bahagian berikut menerangkan LAB dan ALM untuk peranti Intel Agilex.

MAKMAL

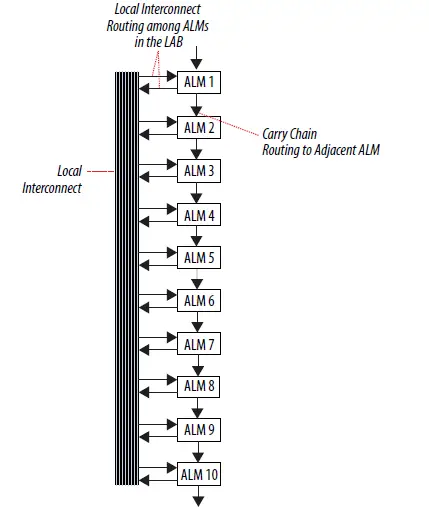

LAB ialah blok logik boleh dikonfigurasikan yang terdiri daripada sekumpulan sumber logik. Setiap LAB mengandungi logik khusus untuk memandu isyarat kawalan kepada ALMnya. MLAB ialah superset LAB dan merangkumi semua ciri LAB. Terdapat sejumlah 10 ALM dalam setiap LAB, seperti yang ditunjukkan dalam Rajah Intel Agilex LAB dan MLAB Structure.

Rajah 1.

Struktur dan Saling Bersambung Intel Agilex LABview

Angka ini menunjukkan tamatview daripada struktur Intel Agilex LAB dan MLAB dengan LAB yang saling bersambung.

Maklumat Berkaitan

Maklumat Berkaitan

MLAB pada halaman 6

MLAB

Setiap MLAB menyokong maksimum 640 bit SRAM dwi-port mudah. Anda boleh mengkonfigurasi setiap ALM dalam MLAB sebagai blok memori 32 (dalam) x 2 (lebar), menghasilkan konfigurasi blok SRAM dwi-port mudah 32 (dalam) x 20 (lebar).

Rajah 2.

Intel Agilex LAB dan Struktur MLAB Sambungan Pautan Setempat dan Terus

Sambungan Pautan Setempat dan Terus

Setiap LAB boleh mengeluarkan 60 output ALM. Subset ini boleh memacu input LAB secara langsung, tetapi sebarang sambungan ke baris atau lajur yang berbeza mesti menggunakan sekurang-kurangnya satu wayar penghalaan tujuan umum.

Sambungan tempatan memacu input ALM. Output ALM, serta sambung lajur dan baris memacu sambung tempatan.

Rajah 3. Intel Agilex LAB Local dan Direct Link Interconnect  Sambungan Rantaian Bawa

Sambungan Rantaian Bawa

Terdapat laluan rantaian bawa khusus antara ALM. Peranti Intel Agilex menyertakan struktur interkoneksi yang dipertingkatkan dalam LAB untuk penghalaan rantai pembawa untuk fungsi aritmetik yang cekap. Sambungan ALM-ke-ALM ini memintas intersambung setempat.

Daftar Intel Hyperflex ditambah pada rantai pembawa untuk membolehkan penamatan fleksibel merentasi rangkaian LAB dan Pengkompil Intel Quartus Prime secara automatik mengambil masa depan.tage sumber ini untuk meningkatkan penggunaan dan prestasi.

Rajah 4. Sambungan Rantaian Bawa Isyarat Kawalan LAB

Isyarat Kawalan LAB

Terdapat dua sumber jam dalam setiap blok kawalan LAB, yang menjana dua jam LAB (LABCLK[1:0]) dan dua jam LAB tertunda (LABCLK_Phi1[1:0]) untuk memacu daftar ALM dan Hyper-Register dalam LAB. LAB menyokong dua isyarat membolehkan jam unik, serta isyarat jelas tambahan, untuk daftar ALM.

Jam baris LAB [5..0] dan sambung tempatan LAB menjana isyarat kawalan seluruh LAB. Rangkaian jam condong rendah mengedarkan isyarat global kepada jam baris [5..0]. Sambungan MultiTrack terdiri daripada talian penghalaan yang dioptimumkan prestasi berterusan dengan panjang dan kelajuan berbeza yang digunakan untuk kecekapan penghalaan. Intel Quartus Prime Compiler secara automatik mengarahkan laluan reka bentuk kritikal pada sambungan yang lebih pantas untuk meningkatkan prestasi reka bentuk dan mengoptimumkan sumber peranti.

Kawalan Logik Kosong

Isyarat seluruh LAB mengawal logik untuk isyarat jelas daftar ALM. Daftar ALM secara langsung menyokong kedua-dua jelas segerak dan tak segerak. Setiap LAB menyokong satu isyarat jelas segerak dan dua isyarat jelas tak segerak.

Peranti Intel Agilex menyediakan pin tetapan semula seluruh peranti (DEV_CLRn) yang menetapkan semula semua daftar dalam peranti. Anda boleh mendayakan pin DEV_CLRn dalam perisian Intel Quartus Prime sebelum penyusunan. Isyarat tetapan semula seluruh peranti mengatasi semua isyarat kawalan lain.

Rajah 5. Isyarat Kawalan Lebar Intel Agilex LAB

ALM

Bahagian berikut merangkumi sumber ALM, output ALM dan mod pengendalian ALM.

Sumber ALM

Setiap ALM mengandungi pelbagai sumber berasaskan LUT yang boleh dibahagikan antara dua LUT penyesuaian gabungan (ALUT), penambah penuh dua bit dan empat daftar.

Dengan sehingga lapan input untuk dua ALUT gabungan, satu ALM boleh melaksanakan pelbagai gabungan dua fungsi. Kebolehsuaian ini membolehkan ALM menjadi serasi sepenuhnya ke belakang dengan empat seni bina LUT input. Satu ALM juga boleh melaksanakan subset lapan fungsi input.

Satu ALM mengandungi empat daftar boleh atur cara. Setiap daftar mempunyai port berikut:

- Data dalam

- Data keluar

- Jam LAB biasa

- Jam LAB tertunda

- Jam membolehkan

- Jelas segerak

- Asynchronous clear

Isyarat global, pin I/O (GPIO) tujuan umum, atau sebarang logik dalaman boleh memacu jam membolehkan isyarat, jam dan isyarat kawalan jelas tak segerak atau segerak bagi daftar ALM. Isyarat pemboleh jam mempunyai keutamaan berbanding isyarat tetapan semula segerak.

Untuk fungsi gabungan, daftar dipintas dan output jadual carian (LUT) dan penambah memacu terus ke output ALM. Dua output pantas tersedia untuk 6 output LUT dan 5 output LUT bawah untuk memintas output mux dan menyambung ke LAB lain untuk pelarasan laluan kritikal.

Rajah 6. Rajah Blok Aras Tinggi Intel Agilex ALM

Keluaran ALM

Keluaran ALM

Output penghalaan umum dalam setiap ALM memacu sumber penghalaan setempat, baris dan lajur. Enam output ALM, termasuk dua laluan keluaran pantas, boleh memacu sambungan penghalaan lajur, baris atau pautan terus.

Keluaran LUT, penambah atau daftar boleh memacu keluaran ALM. Kedua-dua LUT atau penambah dan daftar ALM boleh memandu keluar dari ALM secara serentak.

Pembungkusan daftar meningkatkan penggunaan peranti dengan membenarkan daftar yang tidak berkaitan dan logik gabungan untuk dibungkus ke dalam satu ALM. ALM juga boleh mengeluarkan versi LUT atau output penambah yang berdaftar dan tidak berdaftar.

Rajah berikut menunjukkan sambungan Intel Agilex ALM. Dalam Editor Harta Sumber Intel Quartus Prime, keseluruhan sambungan ALM dipermudahkan. Beberapa penghalaan akan dihalakan secara dalaman oleh perisian Intel Quartus Prime.

Rajah 7. Butiran Sambungan Intel Agilex ALM Mod Operasi ALM

Mod Operasi ALM

Intel Agilex ALM beroperasi dalam mana-mana mod berikut:

- Mod biasa

- Mod LUT lanjutan

- Mod aritmetik

Mod Biasa

Mod biasa membolehkan dua fungsi dilaksanakan dalam satu Intel Agilex ALM, atau satu fungsi sehingga enam input.

Sehingga lapan input data daripada interkoneksi tempatan LAB adalah input kepada logik gabungan.

ALM boleh menyokong gabungan tertentu fungsi bebas sepenuhnya dan pelbagai kombinasi fungsi yang mempunyai input biasa.

Intel Quartus Prime Compiler secara automatik memilih input kepada LUT. ALM dalam mod biasa menyokong pembungkusan daftar.

Rajah berikut menunjukkan gabungan sambungan input yang berbeza untuk mod LUT. Dalam reka bentuk anda, perisian Intel Quartus Prime mungkin menetapkan penamaan input yang berbeza semasa penyusunan.

Rajah 8. ALM dalam Mod Biasa

Gabungan fungsi dengan input yang lebih sedikit daripada yang ditunjukkan juga disokong. Untuk exampOleh itu, gabungan fungsi dengan bilangan input berikut disokong.

- 4 dan 3

- 3 dan 3

- 3 dan 2

- 5 dan 2

Untuk pembungkusan dua fungsi 5-input ke dalam satu ALM, fungsi tersebut mesti mempunyai sekurang-kurangnya dua input biasa. Input biasa ialah dataa dan datab. Gabungan fungsi 4-input dengan fungsi 5-input memerlukan satu input biasa (sama ada dataa atau datab).

Dalam peranti yang jarang digunakan, fungsi yang boleh diletakkan dalam satu ALM boleh dilaksanakan dalam ALM berasingan oleh perisian Intel Quartus Prime untuk mencapai prestasi terbaik. Apabila peranti mula diisi, perisian Intel Quartus Prime secara automatik menggunakan potensi penuh Intel Agilex ALM. Intel Quartus Prime Compiler secara automatik mencari fungsi menggunakan input biasa atau fungsi bebas sepenuhnya untuk diletakkan dalam satu ALM untuk menggunakan sumber peranti dengan cekap. Selain itu, anda boleh mengawal penggunaan sumber secara manual dengan menetapkan penetapan lokasi.

Rajah 9. 6-Input Fungsi Mod LUT dalam Mod Biasa

Rajah 10. 3-Input Fungsi Mod LUT dalam Mod Biasa

Rajah 10. 3-Input Fungsi Mod LUT dalam Mod Biasa

data dan data b tersedia untuk pembungkusan daftar.  Anda boleh melaksanakan mana-mana tiga hingga enam fungsi input menggunakan input berikut:

Anda boleh melaksanakan mana-mana tiga hingga enam fungsi input menggunakan input berikut:

- datae

- datad0

- datac0

- datac1

- datad1

- dataf

- dataa dan datab—dengan mana dataa dan datab dikongsi merentas kedua-dua LUT untuk memberikan fleksibiliti untuk melaksanakan fungsi berbeza dalam setiap LUT.

Kedua-dua input dataa dan datab menyokong ciri pembungkusan daftar. Jika anda mendayakan ciri pembungkusan daftar, kedua-dua input dataa dan datab atau salah satu daripada input memintas LUT dan suapan terus ke dalam daftar, bergantung pada mod daftar pembungkusan yang digunakan. Untuk peranti Intel Agilex, jenis mod daftar padat berikut disokong:

- LUT 5-input dengan 1 laluan daftar padat

- LUT 5-input dengan 2 laluan daftar padat

- Dua LUT 3-input dengan 2 laluan daftar padat

LUT 3-input dengan 2 laluan daftar padat digambarkan dalam Fungsi Mod LUT 3-Input dalam rajah Mod Biasa. Untuk peranti Intel Agilex, mod LUT 6-input tidak menyokong ciri pembungkusan daftar.

Mod LUT Dilanjutkan

Rajah 11. Fungsi 8-Input yang Disokong dalam Mod LUT Lanjutan

Fungsi 8-input tertentu boleh dilaksanakan dalam satu ALM menggunakan semua input LUT:

- datae

- datad0

- datac0

- dataa

- datab

- datac1

- datad1

- dataf

Dalam mod LUT lanjutan 8-input, mod daftar padat disokong, dengan syarat daftar padat berkongsi input dataa atau datab dengan LUT 8-input.

Mod Aritmetik

ALM dalam mod aritmetik menggunakan dua set dua LUT 4-input bersama-sama dengan dua penambah penuh khusus. Penambah khusus membenarkan LUT melakukan logik pra-penambah. Oleh itu, setiap penambah boleh menambah output dua fungsi 4-input.

Mod aritmetik juga menawarkan pembolehan jam, pemboleh balas, kawalan atas dan bawah segerak, kawalan tambah dan tolak, dan jelas segerak.

Pilihan yang jelas dan pemboleh jam ialah isyarat seluruh LAB yang mempengaruhi semua daftar dalam LAB. Anda boleh melumpuhkan atau mendayakan isyarat ini secara individu untuk setiap pasangan daftar dalam LUT adaptif (ALUT). Perisian Intel Quartus Prime secara automatik meletakkan sebarang daftar yang tidak digunakan oleh kaunter ke dalam LAB lain.

Rajah 12. Intel Agilex ALM dalam Mod Aritmetik

Membawa Rantai

Membawa Rantai

Rantaian pembawa menyediakan fungsi bawa pantas antara penambah khusus dalam mod aritmetik.

Ciri pilihan pembawa 2-bit dalam peranti Intel Agilex membahagikan kelewatan penyebaran rantaian pembawa dengan ALM. Rantai pembawa boleh bermula sama ada dalam ALM pertama atau ALM keenam dalam LAB. Isyarat pembawa keluar terakhir dihalakan ke ALM, di mana ia disalurkan ke sambungan setempat, baris atau lajur.

Sejarah Semakan Dokumen untuk Blok Tatasusunan Logik Intel Agilex dan Panduan Pengguna Modul Logik Adaptif

| Versi Dokumen | Perubahan |

| 2022.05.24 | Rajah Dikemaskini: Rajah Blok Aras Tinggi Intel Agilex ALM. |

| 2019.11.14 | Mengemas kini perihalan dalam bahagian Isyarat Kawalan LAB. |

| 2019.10.01 |

|

| 2019.04.02 | Keluaran awal. |

Perbadanan Intel.

Hak cipta terpelihara. Intel, logo Intel dan tanda Intel lain ialah tanda dagangan Intel Corporation atau anak syarikatnya. Intel menjamin prestasi produk FPGA dan semikonduktornya mengikut spesifikasi semasa menurut waranti standard Intel, tetapi berhak untuk membuat perubahan pada mana-mana produk dan perkhidmatan pada bila-bila masa tanpa notis. Intel tidak memikul tanggungjawab atau liabiliti yang timbul daripada aplikasi atau penggunaan mana-mana maklumat, produk atau perkhidmatan yang diterangkan di sini kecuali seperti yang dipersetujui secara bertulis oleh Intel. Pelanggan Intel dinasihatkan untuk mendapatkan versi terkini spesifikasi peranti sebelum bergantung pada sebarang maklumat yang diterbitkan dan sebelum membuat pesanan untuk produk atau perkhidmatan.

*Nama dan jenama lain boleh dituntut sebagai hak milik orang lain.

ISO

9001:2015

Berdaftar

Dokumen / Sumber

|

Blok Tatasusunan Logik Agilex intel dan Modul Logik Adaptif [pdf] Panduan Pengguna Blok Tatasusunan Logik Agilex dan Modul Logik Suaian, Agilex, Blok Tatasusunan Logik dan Modul Logik Suaian, Blok Tatasusunan dan Modul Logik Suaian, Modul Logik Suaian, Modul Logik |