Netlist ViewPanduan Pengguna er

Netlist ViewPanduan Pengguna er

Libero SoC v2024.2

pengenalan (Tanya Soalan)

Apabila reka bentuk Field Programmable Gate Array (FPGA) berkembang dalam saiz dan kerumitan, menjadi penting bagi pereka FPGA untuk melintasi senarai bersih untuk menganalisis reka bentuk mereka. The Microchip Netlist Viewer ialah perwakilan grafik senarai bersih reka bentuk yang memaparkan berbeza views untuk s yang berbezatages daripada proses reka bentuk.

Keluarga dan Platform yang Disokong (Tanya Soalan)

Senarai Net Viewer menyokong peranti keluarga SmartFusion ® 2, IGLOO ® 2, RTG4 ™ , PolarFire ® dan PolarFire SoC serta berjalan pada sistem Windows ® dan Linux ®.

![]() Penting: Bergantung pada peranti yang dipilih, beberapa elemen antara muka pengguna seperti ikon, pilihan, tab dan kotak dialog mungkin berbeza sedikit dalam rupa dan/atau kandungan. Senarai Net Asas Viewkefungsian tetap sama, tanpa mengira peranti yang dipilih. Dalam panduan pengguna ini, peranti PolarFire digunakan dalam bekasample angka.

Penting: Bergantung pada peranti yang dipilih, beberapa elemen antara muka pengguna seperti ikon, pilihan, tab dan kotak dialog mungkin berbeza sedikit dalam rupa dan/atau kandungan. Senarai Net Asas Viewkefungsian tetap sama, tanpa mengira peranti yang dipilih. Dalam panduan pengguna ini, peranti PolarFire digunakan dalam bekasample angka.

Views (Tanya Soalan)

Senarai Net Viewer ialah Antara Muka Pengguna Grafik (GUI) yang memaparkan berbeza views untuk s yang berbezatage daripada proses reka bentuk:

- Daftar Netlist Tahap Pemindahan (RTL). view—menunjukkan cara kod Verilog muncul dalam format reka bentuk.

Menggunakan ini view, anda boleh mengesahkan sama ada perisian melaksanakan logik yang betul. Penyelidikan silang antara ini view dan kod HDL membantu dalam menyelesaikan masalah apabila reka bentuk tidak berfungsi seperti yang dikehendaki. - Hierarki Pasca-Sintesis view-berhierarki view senarai bersih selepas sintesis dan selepas pemetaan teknologi kepada teknologi FPGA Microchip.

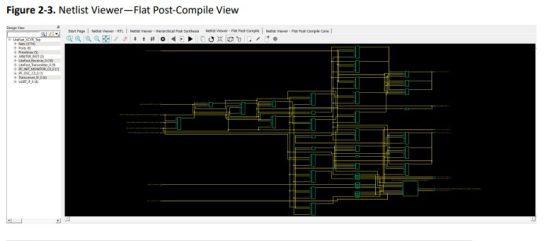

- Senarai Netlist Pasca-Kompil Rata view—senarai bersih yang diratakan selepas sintesis, pemetaan teknologi dan pengoptimuman selanjutnya berdasarkan peraturan Semakan Peraturan Reka Bentuk (DRC) bagi keluarga peranti dan/atau mati.

- Kon Pasca Kompilasi Rata view—memuatkan senarai bersih yang sama seperti Flat Post-Compile view, tetapi pada mulanya tidak melukis apa-apa pada kanvas. Bahagian penting reka bentuk boleh ditambah pada kanvas dari pokok atau daripada item sedia ada dalam view. ini view dibuka lebih cepat daripada Flat Post-Compile view. Ia membolehkan anda memuatkan hanya bahagian reka bentuk yang anda minati. Ini view sangat sesuai digunakan dengan reka bentuk yang besar. ini view tidak tersedia untuk semua keluarga.

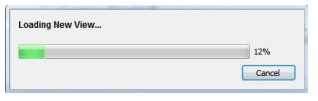

Penting: A bar kemajuan menunjukkan bahawa senarai bersih yang diratakan sedang dimuatkan. Untuk senarai bersih yang besar, pemuatan mungkin dikenakan beberapa penalti masa jalan. Butang Batal tersedia untuk membatalkan pemuatan.

Penting: A bar kemajuan menunjukkan bahawa senarai bersih yang diratakan sedang dimuatkan. Untuk senarai bersih yang besar, pemuatan mungkin dikenakan beberapa penalti masa jalan. Butang Batal tersedia untuk membatalkan pemuatan. Doa (Tanya Soalan)

Doa (Tanya Soalan)

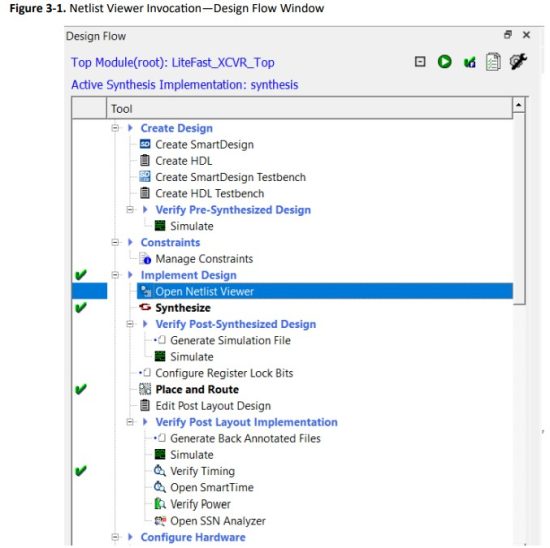

Netlist tersendiri Viewer tersedia untuk permohonan dalam tetingkap Aliran Reka Bentuk. Untuk membuka Netlist kendiri Viewer dalam tetingkap Aliran, lakukan salah satu daripada langkah berikut:

- Klik dua kali Netlist Viewer dalam tetingkap Aliran Reka Bentuk

- Klik kanan Netlist Viewer dan pilih Buka Secara Interaktif

Apabila Netlist Viewer dibuka, ia menyediakan untuk memuatkan dan viewdalam perkara berikut views daripada senarai bersih:

Apabila Netlist Viewer dibuka, ia menyediakan untuk memuatkan dan viewdalam perkara berikut views daripada senarai bersih:

- RTL—tersedia selepas tangkapan reka bentuk/penjanaan reka bentuk

- Hierarki Pasca-Sintesis—tersedia selepas Sintesis

- Flat Post-Compile—tersedia selepas Sintesis atau Tempat dan Laluan. Jika selepas Tempat dan Laluan, Senarai Net Viewer memuatkan Flat Post-Compile view untuk mencerminkan senarai bersih yang dijana selepas Tempat dan Laluan.

- Cone Post-Compile Flat—tersedia selepas Sintesis atau Tempat dan Laluan. Jika selepas Tempat dan Laluan, Senarai Net Viewer memuatkan Flat Post-Compile view untuk mencerminkan senarai bersih yang dihasilkan selepas Tempat dan

Laluan. ini view tidak memaparkan sebarang senarai jaring pada kanvas sehingga contoh daripada pokok reka bentuk dipilih dan dimuatkan. ini view membolehkan anda memuatkan di kawasan khas reka bentuk yang anda minati. Ia juga mengurangkan masa larian.

Netlist Viewe Windows (Tanya Soalan)

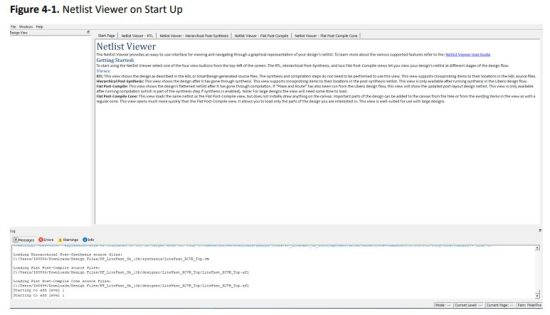

Apabila Netlist yang tersendiri Viewer terbuka, tiada senarai net views dimuatkan. Halaman Mula menunjukkan senarai bersih views yang boleh dibuka untuk viewing.

Senarai Net ViewPanduan Pengguna boleh didapati daripada tetingkap Aliran Reka Bentuk (Netlist Viewer > Help > Netlist Viewer Panduan Pengguna) dan juga dari menu Bantuan (Bantuan > Manual Rujukan).

4.1 Pembukaan a View (Tanya Soalan)

Klik mana-mana yang berikut views di penjuru kiri sebelah atas untuk memuatkan senarai bersih ke dalam Senarai Bersih Vieweh untuk viewing:

- RTL view—Senarai bersih RTL pra-sintesis dilukis dalam view

- Hierarki Pasca-Sintesis view—senarai bersih selepas sintesis dilukis dalam view

Nota: The Hierarki Pasca-Sintesis view tidak tersedia jika sintesis dilumpuhkan dalam aliran reka bentuk (Projek > Tetapan Projek > Aliran Reka Bentuk > Dayakan Sintesis dinyahtanda). - Penyusunan Pasca Rata view—senarai bersih pasca kompil yang diratakan dilukis dalam view

- Kon Pasca Kompilasi Rata view—tiada senarai net dilukis sehingga objek reka bentuk ditambahkan pada view

Penting:

Penting:

- Apabila anda membuka senarai net views buat pertama kali dalam Netlist Viewer, ia dimuatkan ke dalam memori sistem, di mana ia kekal sehingga Netlist Viewer keluar. Untuk reka bentuk yang sangat besar, memuatkan senarai bersih untuk kali pertama mungkin mengambil sedikit masa. Tetingkap pop timbul melaporkan status proses pemuatan.

- Kon Pasca Kompilasi Rata view mengambil masa larian yang sangat sedikit kerana tiada senarai net dibuat apabila ini view mula-mula dimuatkan. ini view tidak memaparkan senarai bersih sehingga kejadian daripada pokok reka bentuk dipilih dan dimuatkan.

Rajah 4-2. Memuatkan Baru View Tetingkap Popup Selepas netlist views dibuka buat kali pertama, ia dimuatkan ke dalam memori sistem, menjadikannya tersedia hampir serta-merta dalam Senarai Bersih Vieweh.

Selepas netlist views dibuka buat kali pertama, ia dimuatkan ke dalam memori sistem, menjadikannya tersedia hampir serta-merta dalam Senarai Bersih Vieweh.

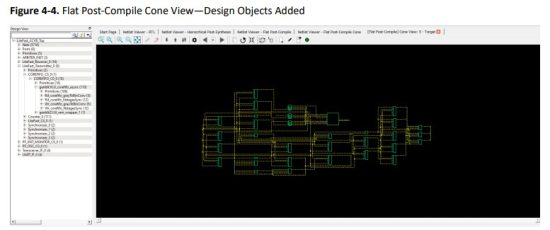

4.1.1 Memaparkan Kon Pasca Kompilasi Rata View (Tanya Soalan)

Apabila Kon Pasca-Kompil Rata view telah selesai memuatkan, tidak seperti tiga yang lain views, tiada apa yang dilukis dalam kanvas. ini view berguna apabila bahagian kecil atau kritikal reka bentuk yang sangat besar perlu diperiksa. Reka bentuk objek yang boleh dipilih untuk paparan dalam ini view termasuk:

ini view berguna apabila bahagian kecil atau kritikal reka bentuk yang sangat besar perlu diperiksa. Reka bentuk objek yang boleh dipilih untuk paparan dalam ini view termasuk:

- Jaring

- Pelabuhan

- Makro

- Komponen

Untuk memaparkan objek reka bentuk dalam Kon Susun Pasca Rata view, klik kanan objek reka bentuk (Jaringan, Makro, Pelabuhan atau Komponen) dalam Pokok Reka Bentuk dan pilih Pilihan Beban. Objek reka bentuk ditambah pada view.

Membuka reka bentuk dalam Flat Post-Compile view boleh dikenakan penalti masa jalan. kon ini view memuatkan sumber senarai bersih AFL yang sama file sebagai Flat Post-Compile view. Walau bagaimanapun, kon ini view, tidak seperti Flat Post-Compile view, tidak menarik apa-apa sehingga anda memilih sebahagian daripada reka bentuk yang anda mahu paparkan. Ini mengurangkan penalti masa jalan yang dikaitkan dengan melukis senarai bersih yang besar untuk paparan. 4.1.1.1 Menambah Jaring (Tanya Soalan)

4.1.1.1 Menambah Jaring (Tanya Soalan)

Klik kanan jaring dalam Pokok Reka Bentuk dan pilih Pilihan Beban untuk menambah jaring pada view. Menambah jaring pada view menambah jaring garisan pepejal pada view (melainkan anda membatalkan lebih awal), termasuk semua kejadian dan port yang disambungkan ke internet. Jaringan tambahan dipilih dalam view.

Jaring yang menjangkau berbilang halaman boleh diikuti melalui item menu klik kanan Ikut Bersih ke Halaman# untuk pergi ke halaman berbeza yang digunakan bersih. 4.1.1.2 Menambah Makro (Tanya Soalan)

4.1.1.2 Menambah Makro (Tanya Soalan)

Makro ialah objek reka bentuk peringkat rendah asas daripada Perpustakaan Makro dalam Katalog. Klik kanan pada makro dalam Pokok Reka Bentuk dan pilih Pilihan Muatan untuk menambah makro. Menambah makro menambah contoh dengan jaring yang disambungkan ke view. Jaring yang disambungkan sentiasa garisan kuning putus-putus, walaupun ia tidak disambungkan kepada mana-mana logik di luar view. Klik dua kali pada jaring menambah sambungan (jika ada) dan mengubah jaring daripada garis putus-putus kepada garisan pepejal. Garis pepejal untuk jaring menunjukkan bahawa ia adalah jaring yang ditambah pengguna. 4.1.1.3 Menambah Port (Tanya Soalan)

4.1.1.3 Menambah Port (Tanya Soalan)

Untuk menambah port pada view, klik kanan port dalam Design Tree dan pilih Load Selection. Menambah port pada view adalah sama seperti menambah jaring yang disambungkan ke port.

4.1.1.4 Menambah Komponen (Tanya Soalan)

Klik kanan komponen dalam Pokok Reka Bentuk dan pilih Pilihan Beban untuk menambah komponen pada view. Menambah komponen pada view adalah sama seperti memilih semua makro peringkat bawah dan menambahkannya pada view. Makro yang ditambahkan dipilih.

Penting: Kepada menjimatkan masa jalan untuk komponen yang sangat besar dengan banyak makro peringkat rendah, makro ditambah, tetapi tidak boleh dipilih.

4.1.1.5 Paparan Muatan/Pemandu (Tanya Soalan)

Objek reka bentuk juga boleh ditambah pada view melalui menu klik kanan untuk menambah beban/pemandu. Tindakan ini menambah sebarang kejadian pada tahap logik yang berbeza.

4.2 Penutup a View (Tanya Soalan)

Untuk menutup yang dibuka view, klik yang dibuka view di bahagian atas Senarai Net Vieweh. A ditutup view kekal dalam memori sistem selagi Netlist Viewer tetap terbuka. Membuka senarai bersih yang sama view pada masa kemudian tidak dikenakan penalti masa jalan, kerana tiada pemuatan diperlukan.

4.3 Senarai Net Viewe Windows (Tanya Soalan)

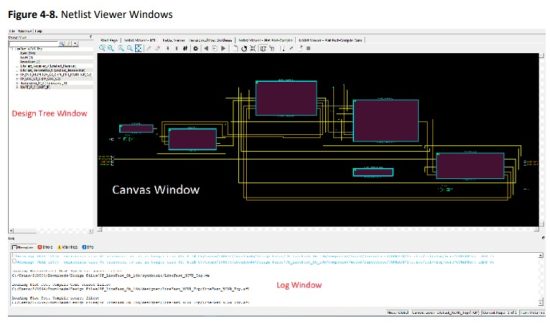

Apabila Netlist Viewer terbuka, ia memaparkan tiga tetingkap secara lalai.

- Tetingkap Design Tree memaparkan hierarki reka bentuk dari peringkat atas.

- Tetingkap kanvas memaparkan senarai bersih views.

- Tetingkap log memaparkan mesej, amaran, maklumat dan sebagainya.

4.4 Reka Bentuk Tingkap Pokok (Tanya Soalan)

4.4 Reka Bentuk Tingkap Pokok (Tanya Soalan)

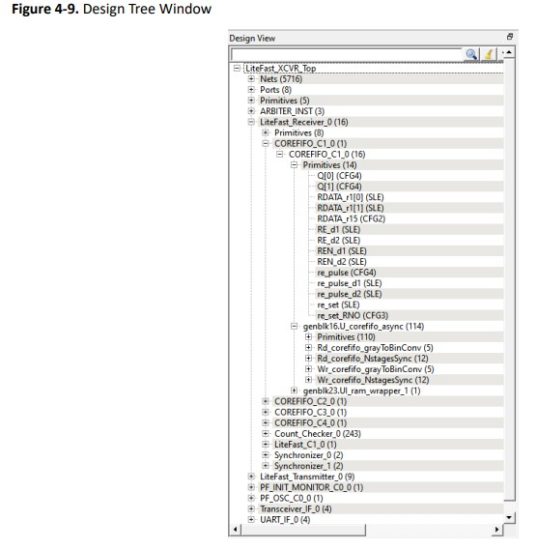

Tetingkap Design Tree memaparkan hierarki reka bentuk dari peringkat atas. Secara lalai, apabila Netlist Viewer terbuka, ia memaparkan tetingkap Design Tree.

Penting: The Tetingkap Design Tree dipaparkan secara lalai apabila Netlist Viewer terbuka. Menyembunyikan Pokok Reka Bentuk view akan meninggalkan lebih banyak kawasan paparan untuk Kanvas view. Untuk mendapatkan kawasan paparan yang lebih besar untuk kanvas view, sembunyikan tetingkap Design Tree (Netlist Viewer > Windows dan nyahtanda Show Tree)

Tetingkap Design Tree memaparkan:

- Jaring ( )—nombor dalam kurungan ialah jumlah bilangan jaring di peringkat atas

- Pelabuhan ( )—nombor dalam kurungan ialah jumlah bilangan port di peringkat atas

- Komponen reka bentuk di bawah peringkat atas—setiap komponen boleh diruntuhkan atau dikembangkan untuk mendedahkan

– Jaring—jumlah bilangan jaring pada tahap komponen

– Port—jumlah bilangan port pada tahap komponen

– Subkomponen di dalam komponen - Nilai Fanout (Jaringan)—apabila dua nombor dipaparkan dalam kurungan, nombor pertama ialah fanout jaring di peringkat tempatan (hierarki) dan nombor kedua ialah fanout jaring di peringkat global. Sebagai bekasample, net_xyz (fanout: 1,3) bermaksud net menuruni tahap hierarki kepada tiga pin berbeza (fanout 3 global) dan tidak disambungkan kepada mana-mana pin lain pada tahap semasa (fanout 1 tempatan).

- Primitif—primitif merujuk kepada makro dan objek reka bentuk peringkat rendah dan boleh muncul di peringkat atas atau peringkat komponen.

Pokok reka bentuk berbeza dengan senarai bersih yang berbeza views. Untuk Penyusun Pasca Rata view, pokok reka bentuk memaparkan bilangan jaring yang jauh lebih besar daripada RTL view atau Hierarki Pasca-Sintesis view, kerana senarai bersih diratakan dalam Post-Compile view dan semua jaring dikira. Jaring dalam Flat Post-Compile view, tidak seperti RTL view atau Hierarki Pasca-Sintesis view, menunjukkan hanya satu nilai untuk fanout (fanout global) kerana ia adalah leper view (tiada hierarki).

Untuk jaring yang merupakan sebahagian daripada NetBundle, nama NetBundle diikuti dengan nombor dalam kurungan yang menunjukkan jumlah bilangan jaring dalam NetBundle. 4.4.1 Penapis (Tanya Soalan)

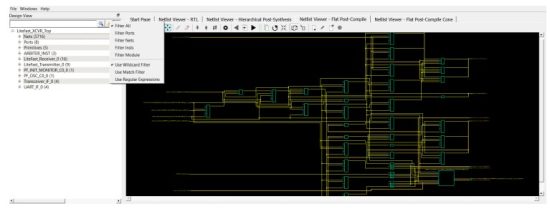

4.4.1 Penapis (Tanya Soalan)

Paparan objek reka bentuk dalam ini view boleh ditapis berdasarkan:

- Ports—memaparkan semua port sahaja, termasuk port tahap komponen.

- Jaring—memaparkan semua jaring sahaja, termasuk jaring peringkat komponen.

- nstances—memaparkan semua kejadian sahaja, termasuk kejadian peringkat komponen.

- Modul—memaparkan semua modul sahaja.

- Tapis Semua—memaparkan semua objek reka bentuk sahaja.

- Gunakan Penapis Wildcard

- Gunakan Penapis Padanan

- Gunakan Ungkapan Biasa

Klik butang Penapis di penjuru kanan sebelah atas Reka Bentuk view untuk menapis objek reka bentuk.

4.4.2 Kebolehoperasian Antara Windows dan Views (Tanya Soalan)

4.4.2 Kebolehoperasian Antara Windows dan Views (Tanya Soalan)

Apabila objek reka bentuk seperti jaring, contoh atau port dipilih dalam tetingkap Pokok Reka Bentuk, objek dipilih dalam senarai bersih yang berbeza views. Begitu juga sebaliknya. Objek yang dipilih dalam satu senarai net view tetingkap juga dipilih dalam tetingkap Design Tree dan netlist lain views.

Saling kendali berfungsi hanya apabila ikon Togol Cross-probing didayakan.

4.5 Tetingkap Kanvas (Tanya Soalan)

Tetingkap Kanvas memaparkan:

- RTL view

- Hierarki Pasca-Sintesis view

- Penyusunan Pasca Rata view

- Kon Pasca Kompilasi Rata view

- kon view

- HDL dibuka files (tidak tersedia dalam Flat Post-Compile view)

- Halaman Mula—apabila tiada senarai net views dibuka

Apabila a view dibuka, a view tab ditambah di bahagian atas tetingkap Kanvas untuk memudahkan pertukaran antara views.

![]() Penting: Kepada dapatkan kawasan paparan yang lebih besar untuk Kanvas view, sembunyikan Reka Bentuk

Penting: Kepada dapatkan kawasan paparan yang lebih besar untuk Kanvas view, sembunyikan Reka Bentuk

Tetingkap Pokok (Netlist Viewer > Windows > Nyahtanda Show Tree) dan sembunyikan tetingkap Log (Netlist Viewer > Windows > Nyahtanda > Tunjukkan Log) Menyembunyikan tetingkap Log dan tetingkap Design Tree meninggalkan lebih banyak kawasan paparan untuk tetingkap Kanvas. Sebagai alternatif, tekan CTRL+W untuk memaksimumkan kawasan kerja. Ikon dalam tetingkap Kanvas membolehkan anda:

Ikon dalam tetingkap Kanvas membolehkan anda:

- Traverse secara menegak ke atas (Pop) atau ke bawah (Tolak) hierarki reka bentuk

- Navigasi secara mendatar merentasi halaman reka bentuk yang berbeza view

- Zum masuk/keluar reka bentuk view

- Jejak jaring kritikal ke pemandu/beban

- Cipta kon logik untuk nyahpepijat

- Kawal paparan warna objek reka bentuk

4.6 Tetingkap Log (Tanya Soalan)

4.6 Tetingkap Log (Tanya Soalan)

Tetingkap Log memaparkan perkara berikut:

- Mesej maklumat seperti lokasi dan nama files digunakan untuk memaparkan view.

- Sebarang ralat sintaks dalam HDL file jika HDL file dibuka dengan Terbuka File Pilihan lokasi (klik kanan objek reka bentuk > Buka File Lokasi).

Penting: The Tetingkap log dipaparkan secara lalai apabila Netlist Viewer terbuka.

Menyembunyikan tetingkap Log akan meninggalkan lebih banyak kawasan paparan untuk Kanvas view. Untuk mendapatkan kawasan paparan yang lebih besar untuk Kanvas view, sembunyikan tetingkap Log (Netlist Viewer > Windows dan nyahtanda (Tunjukkan Log).

4.6.1 Bar Status (Tanya Soalan)

Bar status di sudut kanan bawah Senarai Net Viewer memaparkan perkara berikut:

- Mod—memaparkan mod Global atau Setempat. Mod global bermaksud Senarai Net Viewer boleh merentasi sempadan hierarki apabila mengikut jaring kepada pemandu atau beban. Tempatan bermaksud Senarai Net Viewer tays dalam tahap hierarki reka bentuk semasa.

- Tahap Semasa—memaparkan tahap semasa hierarki reka bentuk, sama ada TOP_LEVEL nama contoh atau nama contoh komponen

- Halaman Semasa—memaparkan halaman semasa Senarai Net Viewer (Halaman x daripada ) apabila merentasi halaman berbeza dari Senarai Net Viewer

- Fam—memaparkan keluarga teknologi

Sejarah Semakan (Tanya Soalan)

Sejarah semakan menerangkan perubahan yang telah dilaksanakan dalam dokumen. Perubahan disenaraikan mengikut semakan, bermula dengan penerbitan terkini.

| Semakan | tarikh | Penerangan |

| M | 08/2024 | Dokumen ini dikeluarkan dengan Libero SoC Design Suite v2024.2 tanpa perubahan daripada v2024.1. |

| L | 08/2023 | Kemas kini editorial sahaja. Tiada kemas kini kandungan teknikal. |

| K | 08/2023 | Kemas kini editorial sahaja. Tiada kemas kini kandungan teknikal. |

| J | 05/2023 | Mengemas kini dokumen dengan grafik berkualiti terkini dan lebih baik. |

| H | 04/2023 | Dokumen ini dikeluarkan dengan Libero SoC Design Suite v2023.1 tanpa perubahan daripada v2022.3. |

| G | 12/2022 | Dokumen ini dikeluarkan dengan Libero SoC Design Suite v2022.3 tanpa perubahan daripada v2022.2. |

| F | 08/2022 | Dokumen ini dikeluarkan dengan Libero SoC Design Suite v2022.2 tanpa perubahan daripada v2022.1. |

| E | 04/2022 | Dokumen ini dikeluarkan dengan Libero SoC Design Suite v2022.1 tanpa perubahan daripada v2021.3. |

| D | 12/2021 | • Dalam bahagian 1. Keluarga dan Platform yang Disokong, menambahkan SoC PolarFire pada senarai peranti yang disokong. • Mengemas kini dokumen dengan kualiti grafik yang lebih baik. |

| C | 08/2021 | Dokumen ini dikeluarkan dengan Libero SoC Design Suite v2021.2 tanpa perubahan daripada v2021.1. |

| B | 04/2021 | Kemas kini editorial sahaja. Tiada kemas kini kandungan teknikal. |

| A | 11/2020 | Dokumen ditukar kepada templat Microchip. |

| 4.0 | 12/2018 | Kemas kini templat dokumen dan suntingan teks kecil |

| 3.0 | 10/2017 | Menambahkan Kon Pasca Kompilasi Rata View |

| 2.0 | 05/2017 | Kemas kini kecil |

| 1.0 | 12/2016 | Semakan Awal |

Sokongan FPGA mikrocip

Kumpulan produk Microchip FPGA menyokong produknya dengan pelbagai perkhidmatan sokongan, termasuk Khidmat Pelanggan, Pusat Sokongan Teknikal Pelanggan, a webtapak, dan pejabat jualan di seluruh dunia.

Pelanggan dicadangkan untuk melawat sumber dalam talian Microchip sebelum menghubungi sokongan kerana kemungkinan besar pertanyaan mereka telah dijawab.

Hubungi Pusat Sokongan Teknikal melalui webtapak di www.microchip.com/support. Sebutkan nombor Bahagian Peranti FPGA, pilih kategori kes yang sesuai dan muat naik reka bentuk files semasa mencipta kes sokongan teknikal.

Hubungi Khidmat Pelanggan untuk mendapatkan sokongan produk bukan teknikal, seperti harga produk, peningkatan produk, maklumat kemas kini, status pesanan dan kebenaran.

- Dari Amerika Utara, hubungi 800.262.1060

- Dari seluruh dunia, hubungi 650.318.4460

- Faks, dari mana-mana sahaja di dunia, 650.318.8044

Maklumat Mikrocip

Microchip itu Webtapak

Microchip menyediakan sokongan dalam talian melalui kami webtapak di www.microchip.com/. ini webtapak digunakan untuk membuat files dan maklumat mudah didapati kepada pelanggan. Beberapa kandungan yang tersedia termasuk:

- Sokongan Produk – Helaian data dan kesilapan, nota aplikasi dan sampprogram, sumber reka bentuk, panduan pengguna dan dokumen sokongan perkakasan, keluaran perisian terkini dan perisian arkib

- Sokongan Teknikal Am – Soalan Lazim (Soalan Lazim), permintaan sokongan teknikal, kumpulan perbincangan dalam talian, penyenaraian ahli program rakan kongsi reka bentuk Microchip

- Perniagaan Microchip – Pemilih produk dan panduan pesanan, siaran akhbar Microchip terkini, penyenaraian seminar dan acara, penyenaraian pejabat jualan Microchip, pengedar dan wakil kilang

Perkhidmatan Pemberitahuan Perubahan Produk

Perkhidmatan pemberitahuan perubahan produk Microchip membantu memastikan pelanggan sentiasa mengetahui produk Microchip. Pelanggan akan menerima pemberitahuan e-mel apabila terdapat perubahan, kemas kini, semakan atau kesilapan yang berkaitan dengan keluarga produk atau alat pembangunan yang diminati.

Untuk mendaftar, pergi ke www.microchip.com/pcn dan ikut arahan pendaftaran.

Sokongan Pelanggan

Pengguna produk Microchip boleh menerima bantuan melalui beberapa saluran:

- Pengedar atau Wakil

- Pejabat Jualan Tempatan

- Jurutera Penyelesaian Terbenam (ESE)

- Sokongan Teknikal

Pelanggan harus menghubungi pengedar, wakil atau ESE mereka untuk mendapatkan sokongan. Pejabat jualan tempatan juga tersedia untuk membantu pelanggan. Penyenaraian pejabat dan lokasi jualan disertakan dalam dokumen ini. Sokongan teknikal boleh didapati melalui webtapak di: www.microchip.com/support

Ciri Perlindungan Kod Peranti Mikrocip

Perhatikan butiran berikut tentang ciri perlindungan kod pada produk Microchip:

- Produk Microchip memenuhi spesifikasi yang terkandung dalam Helaian Data Microchip tertentu mereka.

- Microchip percaya bahawa keluarga produknya selamat apabila digunakan mengikut cara yang dimaksudkan, dalam spesifikasi operasi dan dalam keadaan biasa.

- Nilai mikrocip dan melindungi hak harta inteleknya secara agresif. Percubaan untuk melanggar ciri perlindungan kod produk Microchip adalah dilarang sama sekali dan mungkin melanggar Akta Hak Cipta Milenium Digital.

- Microchip mahupun pengeluar semikonduktor lain tidak boleh menjamin keselamatan kodnya. Perlindungan kod tidak bermakna kami menjamin produk itu "tidak boleh pecah". Perlindungan kod sentiasa berkembang. Microchip komited untuk terus menambah baik ciri perlindungan kod produk kami.

Notis Undang-undang

Penerbitan ini dan maklumat di sini hanya boleh digunakan dengan produk Microchip, termasuk untuk mereka bentuk, menguji dan menyepadukan produk Microchip dengan aplikasi anda. Penggunaan maklumat ini dalam apa-apa cara lain melanggar syarat ini. Maklumat mengenai aplikasi peranti disediakan hanya untuk kemudahan anda dan mungkin digantikan dengan kemas kini. Adalah menjadi tanggungjawab anda untuk memastikan permohonan anda memenuhi spesifikasi anda. Hubungi pejabat jualan Microchip tempatan anda untuk mendapatkan sokongan tambahan atau, dapatkan sokongan tambahan di www.microchip.com/en-us/support/design-help/client-support-services.

MAKLUMAT INI DISEDIAKAN OLEH MICROCHIP "SEBAGAIMANA ADANYA". MICROCHIP TIDAK MEMBUAT SEBARANG JENIS PERWAKILAN ATAU WARANTI SAMA ADA TERNYATA MAUPUN TERSIRAT, BERTULIS ATAU LISAN, BERKANUN ATAU SEBALIKNYA, BERKAITAN DENGAN MAKLUMAT TERMASUK TETAPI TIDAK TERHAD KEPADA MANA-MANA WARANTI TERSIRAT, BUKAN PENYERTAAN DAN PEMESANAN TUJUAN ATAU WARANTI BERKAITAN DENGAN KEADAAN, KUALITI ATAU PRESTASINYA.

MICROCHIP TIDAK AKAN AKAN BERTANGGUNGJAWAB KE ATAS SEBARANG KERUGIAN, KEROSAKAN, KOS ATAU AKIBAT YANG TIDAK LANGSUNG, KHAS, PUNITIF, SAMPINGAN ATAU AKIBAT APA-APA JENIS APA SAJA YANG BERKAITAN DENGAN MAKLUMAT ATAU PENGGUNAANNYA, WALAUPUN BERPUNCA, WALAUPUN TERJADI. KEMUNGKINAN ATAU KEROSAKAN ADALAH BOLEH DIRAMALKAN. SEJAUH YANG DIBENARKAN OLEH UNDANG-UNDANG, JUMLAH LIABILITI MICROCHIP ATAS SEMUA TUNTUTAN DALAM APA-APA CARA BERKAITAN DENGAN MAKLUMAT ATAU PENGGUNAANNYA TIDAK AKAN MELEBIHI JUMLAH YURAN, JIKA ADA, YANG ANDA TELAH BAYAR TERUS KEPADA MICROCHIP UNTUK MAKLUMAT.

Penggunaan peranti Microchip dalam sokongan hayat dan/atau aplikasi keselamatan adalah sepenuhnya atas risiko pembeli, dan pembeli bersetuju untuk mempertahankan, menanggung rugi dan menahan Microchip yang tidak berbahaya daripada sebarang dan semua kerosakan, tuntutan, saman atau perbelanjaan akibat daripada penggunaan tersebut. Tiada lesen disampaikan, secara tersirat atau sebaliknya, di bawah mana-mana hak harta intelek Microchip melainkan dinyatakan sebaliknya.

Tanda dagangan

Nama dan logo Microchip, logo Microchip, Adaptec, AVR, logo AVR, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch MediaLB, megaAVR, Microsemi, logo Microsemi, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, logo PIC32, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom , SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron dan XMEGA ialah tanda dagangan berdaftar Microchip Technology Incorporated di Amerika Syarikat dan negara lain.

AgileSwitch, ClockWorks, Syarikat Penyelesaian Kawalan Terbenam, EtherSynch, Flashtec, Kawalan Kelajuan Hiper, Beban HyperLight, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, logo ProASIC Plus, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider dan ZL ialah tanda dagangan berdaftar Microchip Technology Incorporated di Amerika Syarikat

Penindasan Kunci Bersebelahan, AKS, Analog-untuk-Digital Age, Mana-mana Kapasitor, AnyIn, AnyOut, Pensuisan Ditambah, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net Padanan Purata Dynamic , DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge, IGaT, Pengaturcaraan Bersiri Dalam Litar, ICSP, INICnet, Pintar Selari, IntelliMOS, Kesambungan Antara Cip, JitterBlocker, Tombol pada Paparan, Pautan Margin, maxC maksView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Penjanaan Kod Omniscient, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon , QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-IS, storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance , Masa Dipercayai, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect dan ZENA ialah tanda dagangan Microchip Technology Incorporated di Amerika Syarikat dan negara lain.

SQTP ialah tanda perkhidmatan Microchip Technology Incorporated di Amerika Syarikat

Logo Adaptec, Frequency on Demand, Silicon Storage Technology dan Symmcom ialah tanda dagangan berdaftar Microchip Technology Inc. di negara lain.

GestIC ialah tanda dagangan berdaftar Microchip Technology Germany II GmbH & Co. KG, anak syarikat Microchip Technology Inc., di negara lain.

Semua tanda dagangan lain yang disebut di sini adalah hak milik syarikat masing-masing.

2024, Microchip Technology Incorporated dan anak syarikatnya. Hak Cipta Terpelihara.

ISBN: 978-1-6683-4746-1 ©

Sistem Pengurusan Kualiti

Untuk maklumat mengenai Sistem Pengurusan Kualiti Microchip, sila lawati www.microchip.com/quality.

Jualan dan Perkhidmatan Seluruh Dunia

| AMERIKA | ASIA/PASIFIK | ASIA/PASIFIK | EROPAH |

| Pejabat Korporat 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Faks: 480-792-7277 Sokongan Teknikal: www.microchip.com/support Web Alamat: www.microchip.com Atlanta Duluth, GA Tel: 678-957-9614 Faks: 678-957-1455 Austin, TX Tel: 512-257-3370 Boston Westborough, MA Tel: 774-760-0087 Faks: 774-760-0088 Chicago Itasca, IL Tel: 630-285-0071 Faks: 630-285-0075 Dallas Addison, TX Tel: 972-818-7423 Faks: 972-818-2924 Detroit Novi, MI Tel: 248-848-4000 Houston, TX Tel: 281-894-5983 Indianapolis Noblesville, IN Tel: 317-773-8323 Faks: 317-773-5453 Tel: 317-536-2380 Los Angeles Mission Viejo, CA Tel: 949-462-9523 Faks: 949-462-9608 Tel: 951-273-7800 Raleigh, NC Tel: 919-844-7510 New York, NY Tel: 631-435-6000 San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270 Kanada - Toronto Tel: 905-695-1980 Faks: 905-695-2078 |

Australia – Sydney Tel: 61-2-9868-6733 China - Beijing Tel: 86-10-8569-7000 China – Chengdu Tel: 86-28-8665-5511 China – Chongqing Tel: 86-23-8980-9588 China - Dongguan Tel: 86-769-8702-9880 China - Guangzhou Tel: 86-20-8755-8029 China - Hangzhou Tel: 86-571-8792-8115 China – Hong Kong SAR Tel: 852-2943-5100 China - Nanjing Tel: 86-25-8473-2460 China – Qingdao Tel: 86-532-8502-7355 China - Shanghai Tel: 86-21-3326-8000 China - Shenyang Tel: 86-24-2334-2829 China - Shenzhen Tel: 86-755-8864-2200 China - Suzhou Tel: 86-186-6233-1526 China - Wuhan Tel: 86-27-5980-5300 China – Xian Tel: 86-29-8833-7252 China - Xiamen Tel: 86-592-2388138 China – Zhuhai Tel: 86-756-3210040 |

India – Bangalore Tel: 91-80-3090-4444 India – New Delhi Tel: 91-11-4160-8631 India - Pune Tel: 91-20-4121-0141 Jepun - Osaka Tel: 81-6-6152-7160 Jepun - Tokyo Tel: 81-3-6880-3770 Korea - Daegu Tel: 82-53-744-4301 Korea - Seoul Tel: 82-2-554-7200 Malaysia – Kuala Lumpur Tel: 60-3-7651-7906 Malaysia – Pulau Pinang Tel: 60-4-227-8870 Filipina – Manila Tel: 63-2-634-9065 Singapura Tel: 65-6334-8870 Taiwan – Hsin Chu Tel: 886-3-577-8366 Taiwan – Kaohsiung Tel: 886-7-213-7830 Taiwan - Taipei Tel: 886-2-2508-8600 Thailand – Bangkok Tel: 66-2-694-1351 Vietnam – Ho Chi Minh Tel: 84-28-5448-2100 |

Austria - Wels Tel: 43-7242-2244-39 Faks: 43-7242-2244-393 Denmark – Copenhagen Tel: 45-4485-5910 Faks: 45-4485-2829 Finland – Espoo Tel: 358-9-4520-820 Perancis - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Jerman - Garching Tel: 49-8931-9700 Jerman – Haan Tel: 49-2129-3766400 Jerman - Heilbronn Tel: 49-7131-72400 Jerman - Karlsruhe Tel: 49-721-625370 Jerman - Munich Tel: 49-89-627-144-0 Fax: 49-89-627-144-44 Jerman - Rosenheim Tel: 49-8031-354-560 Israel – Ra'anana Tel: 972-9-744-7705 Itali - Milan Tel: 39-0331-742611 Faks: 39-0331-466781 Itali - Padova Tel: 39-049-7625286 Belanda – Drunen Tel: 31-416-690399 Faks: 31-416-690340 Norway - Trondheim Tel: 47-72884388 Poland – Warsaw Tel: 48-22-3325737 Romania – Bucharest Tel: 40-21-407-87-50 Sepanyol - Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 Sweden - Gothenberg Tel: 46-31-704-60-40 Sweden – Stockholm Tel: 46-8-5090-4654 UK – Wokingham Tel: 44-118-921-5800 Faks: 44-118-921-5820 |

Dokumen / Sumber

|

MICROCHIP v2024.2 Libero SoC Design Suite [pdf] Panduan Pengguna v2024.2, 12.0, v2024.2 Libero SoC Design Suite, v2024.2, Libero SoC Design Suite, SoC Design Suite, Design Suite, Suite |