ARTIX-7 FPGA

Papan Teras

AC7A200

Sistem pada Modul

Manual Pengguna

Rekod Versi

| Versi | tarikh | Keluaran Oleh | Penerangan |

| Wahyu 1.0 | 28-06-20 | Rachel Zhou | Keluaran Pertama |

Bahagian 1: Pengenalan Papan Teras AC7A200

AC7A200 (model papan teras, sama di bawah) Papan teras FPGA, ia berdasarkan siri ARTIX-7 XILINX 100T XC7A200T-2FBG484I. Ia adalah papan teras berprestasi tinggi dengan kelajuan tinggi, lebar jalur tinggi dan kapasiti tinggi. Ia sesuai untuk komunikasi data berkelajuan tinggi, pemprosesan imej video, pemerolehan data berkelajuan tinggi dll.

Papan teras AC7A200 ini menggunakan dua keping cip DDR41 MT256J16M125HA-3 MICRON, setiap DDR mempunyai kapasiti 4Gbit; dua cip DDR digabungkan menjadi lebar bas data 32-bit, dan lebar jalur data baca/tulis antara FPGA dan DDR3 adalah sehingga 25Gb; konfigurasi sedemikian boleh memenuhi keperluan pemprosesan data jalur lebar yang tinggi.

Papan teras AC7A200 mengembangkan 180 port IO standard tahap 3.3V, 15 port IO standard tahap 1.5V dan 4 pasang isyarat pembezaan RX/TX berkelajuan tinggi GTP. Bagi pengguna yang memerlukan banyak IO, papan teras ini akan menjadi pilihan yang baik. Selain itu, penghalaan antara cip FPGA dan antara muka adalah sama panjang dan pemprosesan berbeza, dan saiz papan teras hanya 2.36 inci *2.36 inci, yang sangat sesuai untuk pembangunan sekunder.

Rajah 1-1: Papan Teras AC7A200 (Hadapan View)

Rajah 1-2: Papan Teras AC7A200 (Belakang View)

Bahagian 2: Cip FPGA

Seperti yang dinyatakan di atas, model FPGA yang kami gunakan ialah XC7A200T-2FBG484I, yang dimiliki oleh siri Artix-7 Xilinx. Gred kelajuan ialah 2, dan gred suhu ialah gred industri. Model ini ialah pakej FGG484 dengan 484 pin. Peraturan penamaan cip Xilinx ARTIX-7 FPGA seperti di bawah

Rajah 2-1: Definisi Model Cip Khusus Siri ARTIX-7

Rajah 2-2: Cip FPGA di atas kapal

Parameter utama cip FPGA XC7A200T adalah seperti berikut

| Nama | Parameter khusus |

| Sel Logik | 215360 |

| hirisan | 16-02-92 |

| Selipar CLB | 269200 |

| Sekat RAM(kb) | 13140 |

| Kepingan DSP | 740 |

| PCIe Gen2 | 1 |

| XADC | 1 XADC, 12bit, 1Mbps AD |

| Pemindah GTP | 4 GTP, 6.6Gb/s maks |

| Gred Kelajuan | -2 |

| Gred Suhu | Perindustrian |

Sistem bekalan kuasa FPGA

Bekalan kuasa FPGA Artix-7 ialah VCCINT, VCCBRAM, VCCAUX, VCCO, VMGTAVCC dan VMGTAVTT. VCCINT ialah pin bekalan kuasa teras FPGA, yang perlu disambungkan kepada 1.0V; VCCBRAM ialah pin bekalan kuasa FPGA Block RAM, sambungkan kepada 1.0V; VCCAUX ialah pin bekalan kuasa tambahan FPGA, sambungkan 1.8V; VCCO ialah voltage setiap BANK FPGA, termasuk BANK0, BANK13~16, BANK34~35. Pada papan teras FPGA AC7A200, BANK34 dan BANK35 perlu disambungkan ke DDR3, voltage sambungan BANK ialah 1.5V, dan voltage BANK lain ialah 3.3V. VCCO BANK15 dan BANK16 dikuasakan oleh LDO, dan boleh ditukar dengan menggantikan cip LDO. VMGTAVCC ialah bekalan voltage transceiver GTP dalaman FPGA, disambungkan kepada 1.0V; VMGTAVTT ialah vol penamatantage transceiver GTP, disambungkan kepada 1.2V.

Sistem FPGA Artix-7 memerlukan jujukan kuasa dikuasakan oleh VCCINT, kemudian VCCBRAM, kemudian VCCAUX, dan akhirnya VCCO. Jika VCCINT dan VCCBRAM mempunyai vol yang samatage, mereka boleh dikuasakan pada masa yang sama. Perintah kuasa outages diterbalikkan. Urutan kuasa bagi transceiver GTP ialah VCCINT, kemudian VMGTAVCC, kemudian VMGTAVTT. Jika VCCINT dan VMGTAVCC mempunyai vol yang samatage, mereka boleh dikuasakan pada masa yang sama. Urutan pemadaman kuasa adalah bertentangan dengan urutan hidupkan kuasa.

Bahagian 3: Kristal Pembezaan Aktif

Papan teras AC7A200 dilengkapi dengan dua kristal pembezaan aktif Sitime, satu ialah 200MHz, modelnya ialah SiT9102-200.00MHz, jam utama sistem untuk FPGA dan digunakan untuk menjana jam kawalan DDR3; yang lain ialah 125MHz, model ialah SiT9102 -125MHz, input jam rujukan untuk transceiver GTP.

Bahagian 3.1: Jam Pembezaan Aktif 200Mhz

G1 dalam Rajah 3-1 ialah kristal pembezaan aktif 200M yang menyediakan sumber jam sistem papan pembangunan. Output kristal disambungkan kepada pin jam global BANK34 MRCC (R4 dan T4) FPGA. Jam pembezaan 200Mhz ini boleh digunakan untuk memacu logik pengguna dalam FPGA. Pengguna boleh mengkonfigurasi PLL dan DCM di dalam FPGA untuk menjana jam frekuensi yang berbeza.

Rajah 3-1: Skema Kristal Pembezaan Aktif 200Mhz

Rajah 3-2: Kristal Pembezaan Aktif 200Mhz pada Papan Teras

Tugasan Pin Jam Berbeza 200Mhz

| Nama Isyarat | PIN FPGA |

| SYS_CLK_P | R4 |

| SYS_CLK_N | T4 |

Bahagian 3.2: Kristal Pembezaan Aktif 125MHz

G2 dalam Rajah 3-3 ialah kristal pembezaan aktif 125MHz, yang merupakan jam input rujukan yang diberikan kepada modul GTP di dalam FPGA. Output kristal disambungkan kepada pin jam GTP BANK216 MGTREFCLK0P (F6) dan MGTREFCLK0N (E6) FPGA.

Rajah 3-3: Skema Kristal Pembezaan Aktif 125MHz

Rajah 3-4: Kristal Pembezaan Aktif 125MHz pada Papan Teras

Tugasan Pin Jam Berbeza 125MHz

| Nama Bersih | PIN FPGA |

| MGT_CLK0_P | F6 |

| MGT_CLK0_N | E6 |

Bahagian 4: DRAM DDR3

Papan teras FPGA AC7A200 dilengkapi dengan dua cip DDR4 Micron 512Gbit (3MB) (8Gbit sepenuhnya), modelnya ialah MT41J256M16HA-125 (serasi dengan MT41K256M16HA-125). DDR3 SDRAM mempunyai kelajuan operasi maksimum 400MHz (kadar data 800Mbps). Sistem memori DDR3 disambungkan terus ke antara muka memori BANK 34 dan BANK35 FPGA. Konfigurasi khusus DDR3 SDRAM ditunjukkan dalam Jadual 4-1.

| Nombor Bit | Model Cip | Kapasiti | Kilang |

| U5,U6 | MT41J256M16HA-125 | 256M x 16bit | Mikron |

Jadual 4-1: Konfigurasi DDR3 SDRAM

Reka bentuk perkakasan DDR3 memerlukan pertimbangan yang ketat terhadap integriti isyarat. Kami telah mempertimbangkan sepenuhnya rintangan perintang/terminal yang sepadan, kawalan impedans surih dan kawalan panjang surih dalam reka bentuk litar dan reka bentuk PCB untuk memastikan operasi DDR3 berkelajuan tinggi dan stabil. Rajah 4-1 memperincikan sambungan perkakasan DDR3 DRAM

Rajah 4-1: Skema DDR3 DRAM

Rajah 4-2: DDR3 pada Papan Teras

Tugasan pin DRAM DDR3:

| Nama Bersih | Nama PIN FPGA | FPGA P/N |

| DDR3_DQS0_P | IO_L3P_T0_DQS_AD5P_35 | E1 |

| DDR3_DQS0_N | IO_L3N_T0_DQS_AD5N_35 | D1 |

| DDR3_DQS1_P | IO_L9P_T1_DQS_AD7P_35 | K2 |

| DDR3_DQS1_N | IO_L9N_T1_DQS_AD7N_35 | J2 |

| DDR3_DQS2_P | IO_L15P_T2_DQS_35 | M1 |

| DDR3_DQS2_N | IO_L15N_T2_DQS_35 | L1 |

| DDR3_DQS3_P | IO_L21P_T3_DQS_35 | P5 |

| DDR3_DQS3_N | IO_L21N_T3_DQS_35 | P4 |

| DDR3_DQ[0] | IO_L2P_T0_AD12P_35 | C2 |

| DDR3_DQ [1] | IO_L5P_T0_AD13P_35 | G1 |

| DDR3_DQ [2] | IO_L1N_T0_AD4N_35 | A1 |

| DDR3_DQ [3] | IO_L6P_T0_35 | F3 |

| DDR3_DQ [4] | IO_L2N_T0_AD12N_35 | B2 |

| DDR3_DQ [5] | IO_L5N_T0_AD13N_35 | F1 |

| DDR3_DQ [6] | IO_L1P_T0_AD4P_35 | B1 |

| DDR3_DQ [7] | IO_L4P_T0_35 | E2 |

| DDR3_DQ [8] | IO_L11P_T1_SRCC_35 | H3 |

| DDR3_DQ [9] | IO_L11N_T1_SRCC_35 | G3 |

| DDR3_DQ [10] | IO_L8P_T1_AD14P_35 | H2 |

| DDR3_DQ [11] | IO_L10N_T1_AD15N_35 | H5 |

| DDR3_DQ [12] | IO_L7N_T1_AD6N_35 | J1 |

| DDR3_DQ [13] | IO_L10P_T1_AD15P_35 | J5 |

| DDR3_DQ [14] | IO_L7P_T1_AD6P_35 | K1 |

| DDR3_DQ [15] | IO_L12P_T1_MRCC_35 | H4 |

| DDR3_DQ [16] | IO_L18N_T2_35 | L4 |

| DDR3_DQ [17] | IO_L16P_T2_35 | M3 |

| DDR3_DQ [18] | IO_L14P_T2_SRCC_35 | L3 |

| DDR3_DQ [19] | IO_L17N_T2_35 | J6 |

| DDR3_DQ [20] | IO_L14N_T2_SRCC_35 | K3 |

| DDR3_DQ [21] | IO_L17P_T2_35 | K6 |

| DDR3_DQ [22] | IO_L13N_T2_MRCC_35 | J4 |

| DDR3_DQ [23] | IO_L18P_T2_35 | L5 |

| DDR3_DQ [24] | IO_L20N_T3_35 | P1 |

| DDR3_DQ [25] | IO_L19P_T3_35 | N4 |

| DDR3_DQ [26] | IO_L20P_T3_35 | R1 |

| DDR3_DQ [27] | IO_L22N_T3_35 | N2 |

| DDR3_DQ [28] | IO_L23P_T3_35 | M6 |

| DDR3_DQ [29] | IO_L24N_T3_35 | N5 |

| DDR3_DQ [30] | IO_L24P_T3_35 | P6 |

| DDR3_DQ [31] | IO_L22P_T3_35 | P2 |

| DDR3_DM0 | IO_L4N_T0_35 | D2 |

| DDR3_DM1 | IO_L8N_T1_AD14N_35 | G2 |

| DDR3_DM2 | IO_L16N_T2_35 | M2 |

| DDR3_DM3 | IO_L23N_T3_35 | M5 |

| DDR3_A[0] | IO_L11N_T1_SRCC_34 | AA4 |

| DDR3_A[1] | IO_L8N_T1_34 | AB2 |

| DDR3_A[2] | IO_L10P_T1_34 | AA5 |

| DDR3_A[3] | IO_L10N_T1_34 | AB5 |

| DDR3_A[4] | IO_L7N_T1_34 | AB1 |

| DDR3_A[5] | IO_L6P_T0_34 | U3 |

| DDR3_A[6] | IO_L5P_T0_34 | W1 |

| DDR3_A[7] | IO_L1P_T0_34 | T1 |

| DDR3_A[8] | IO_L2N_T0_34 | V2 |

| DDR3_A[9] | IO_L2P_T0_34 | U2 |

| DDR3_A[10] | IO_L5N_T0_34 | Y1 |

| DDR3_A[11] | IO_L4P_T0_34 | W2 |

| DDR3_A[12] | IO_L4N_T0_34 | Y2 |

| DDR3_A[13] | IO_L1N_T0_34 | U1 |

| DDR3_A[14] | IO_L6N_T0_VREF_34 | V3 |

| DDR3_BA[0] | IO_L9N_T1_DQS_34 | AA3 |

| DDR3_BA[1] | IO_L9P_T1_DQS_34 | Y3 |

| DDR3_BA[2] | IO_L11P_T1_SRCC_34 | Y4 |

| DDR3_S0 | IO_L8P_T1_34 | AB3 |

| DDR3_RAS | IO_L12P_T1_MRCC_34 | V4 |

| DDR3_CAS | IO_L12N_T1_MRCC_34 | W4 |

| DDR3_WE | IO_L7P_T1_34 | AA1 |

| DDR3_ODT | IO_L14N_T2_SRCC_34 | U5 |

| DDR3_RESET | IO_L15P_T2_DQS_34 | W6 |

| DDR3_CLK_P | IO_L3P_T0_DQS_34 | R3 |

| DDR3_CLK_N | IO_L3N_T0_DQS_34 | R2 |

| DDR3_CKE | IO_L14P_T2_SRCC_34 | T5 |

Bahagian 5: Denyar QSPI

Papan teras FPGA AC7A200 dilengkapi dengan satu 128Mbit QSPI FLASH, dan modelnya ialah N25Q128, yang menggunakan vol 3.3V CMOStage standard. Oleh kerana sifat QSPI FLASH yang tidak meruap, ia boleh digunakan sebagai peranti but untuk sistem menyimpan imej but sistem. Imej ini terutamanya termasuk bit FPGA files, kod aplikasi ARM, kod aplikasi teras lembut dan data pengguna lain files. Model khusus dan parameter berkaitan SPI FLASH ditunjukkan dalam Jadual 5-1.

| kedudukan | Model | Kapasiti | Kilang |

| U8 | N25Q128 | 128M Bit | Numonyx |

Jadual 5-1: Spesifikasi QSPI FLASH

QSPI FLASH disambungkan kepada pin khusus BANK0 dan BANK14 cip FPGA. Pin jam disambungkan ke CCLK0 BANK0, dan isyarat pilih data dan cip lain masing-masing disambungkan ke pin D00~D03 dan FCS BANK14. Rajah 5-1 menunjukkan sambungan perkakasan QSPI Flash.

Rajah 5-1: Skema Flash QSPI

Tugasan pin Flash QSPI:

| Nama Bersih | Nama PIN FPGA | FPGA P/N |

| QSPI_CLK | CCLK_0 | L12 |

| QSPI_CS | IO_L6P_T0_FCS_B_14 | T19 |

| QSPI_DQ0 | IO_L1P_T0_D00_MOSI_14 | P22 |

| QSPI_DQ1 | IO_L1N_T0_D01_DIN_14 | R22 |

| QSPI_DQ2 | IO_L2P_T0_D02_14 | P21 |

| QSPI_DQ3 | IO_L2N_T0_D03_14 | R21 |

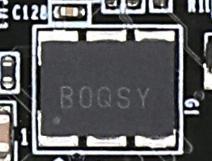

Rajah 5-2: QSPI FLASH pada Papan Teras

Bahagian 6: Lampu LED pada Papan Teras

Terdapat 3 lampu LED merah pada papan teras AC7A200 FPGA, salah satunya ialah lampu penunjuk kuasa (PWR), satu lampu LED konfigurasi (DONE), dan satu lampu LED pengguna. Apabila papan teras dikuasakan, penunjuk kuasa akan menyala; apabila FPGA dikonfigurasikan, LED konfigurasi akan menyala. Lampu LED pengguna disambungkan ke IO BANK34, pengguna boleh mengawal lampu hidup dan mati oleh program. Apabila IO voltage disambungkan kepada LED pengguna adalah tinggi, LED pengguna menyala. Apabila sambungan IO voltage rendah, LED pengguna akan dipadamkan. Gambar rajah skema sambungan perkakasan lampu LED ditunjukkan dalam Rajah 6-1:

Rajah 6-1: Lampu LED pada Skema Papan Teras

Rajah 6-2: Lampu LED pada Papan Teras

Tugasan Pin LED Pengguna

| Nama Isyarat | Nama Pin FPGA | Nombor Pin FPGA | Penerangan |

| LED1 | IO_L15N_T2_DQS_34 | W5 | LED pengguna |

Bahagian 7: JTAG Antara muka

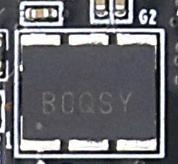

JTAG soket ujian J1 dikhaskan pada papan teras AC7A200 untuk JTAG muat turun dan nyahpepijat apabila papan teras digunakan secara bersendirian. Rajah 7-1 ialah bahagian skematik JTAG port, yang melibatkan TMS, TDI, TDO, TCK. , GND, +3.3V enam isyarat ini.

Rajah 7-1: JTAG Skema Antara Muka

JTAG antara muka J1 pada papan teras FPGA AC7A200 menggunakan lubang ujian satu baris padang 6-pin 2.54mm. Jika anda perlu menggunakan JTAG penyambung untuk nyahpepijat pada papan teras, anda perlu menyolder pengepala pin baris tunggal 6-pin.

Rajah 7-2 menunjukkan JTAG antara muka J1 pada papan teras FPGA AC7A200.

Rajah 7-2 JTAG Antara muka pada Papan Teras

Bahagian 8: Antara Muka Kuasa pada Papan Teras

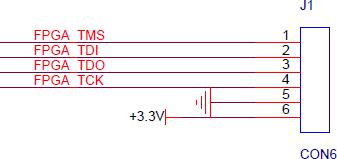

Untuk menjadikan papan teras AC7A200 FPGA berfungsi sahaja, papan teras dikhaskan antara muka bekalan kuasa 2-pin J2. Jika pengguna ingin menyahpepijat fungsi papan teras secara berasingan (tanpa papan pembawa), peranti luaran perlu menyediakan +5V untuk membekalkan kuasa kepada papan teras.

Rajah 8-1:Skema Antara Muka Kuasa pada Papan Teras

Rajah 8-2:Antara muka kuasa pada Papan Teras

Bahagian 9: Tugasan pin Penyambung Papan ke Papan

Papan teras mempunyai sejumlah empat penyambung papan ke papan berkelajuan tinggi.

Papan teras menggunakan empat penyambung antara papan 80-pin untuk menyambung ke papan pembawa. Port IO FPGA disambungkan kepada empat penyambung melalui penghalaan pembezaan. Jarak pin penyambung ialah 0.5mm, masukkan ke papan ke penyambung papan pada papan pembawa untuk komunikasi data berkelajuan tinggi.

Penyambung Papan ke Papan CON1

Papan 80-pin ke papan penyambung CON1, yang digunakan untuk menyambung dengan bekalan kuasa VCCIN (+5V) dan dibumikan pada papan pembawa, memanjangkan IO biasa FPGA. Perlu diingatkan di sini bahawa 15 pin CON1 disambungkan ke port IO BANK34, kerana sambungan BANK34 disambungkan ke DDR3. Oleh itu, voltagstandard bagi semua IO BANK34 ini ialah 1.5V.

Penyerahan Pin Papan kepada Penyambung Papan CON1

| CON1 PIN |

bersih Nama |

FPGA PIN |

Voltage Tahap |

CON1 PIN |

bersih Nama |

FPGA PIN |

Voltage Tahap |

| PIN1 | VCCIN | – | +5V | PIN2 | VCCIN | – | +5V |

| PIN3 | VCCIN | – | +5V | PIN4 | VCCIN | – | +5V |

| PIN5 | VCCIN | – | +5V | PIN6 | VCCIN | – | +5V |

| PIN7 | VCCIN | – | +5V | PIN8 | VCCIN | – | +5V |

| PIN9 | GND | – | tanah | PIN10 | GND | – | tanah |

| PIN11 | NC | – | NC | PIN12 | NC | – | NC |

| PIN13 | NC | – | NC | PIN14 | NC | – | NC |

| PIN15 | NC | – | NC | PIN16 | B13_L4_P | AA15 | 3.3V |

| PIN17 | NC | – | NC | PIN18 | B13_L4_N | AB15 | 3.3V |

| PIN19 | GND | – | tanah | PIN20 | GND | – | tanah |

| PIN21 | B13_L5_P | Y13 | 3.3V | PIN22 | B13_L1_P | Y16 | 3.3V |

| PIN23 | B13_L5_N | AA14 | 3.3V | PIN24 | B13_L1_N | AA16 | 3.3V |

| PIN25 | B13_L7_P | AB11 | 3.3V | PIN26 | B13_L2_P | AB16 | 3.3V |

| PIN27 | B13_L7_P | AB12 | 3.3V | PIN28 | B13_L2_N | AB17 | 3.3V |

| PIN29 | GND | – | tanah | PIN30 | GND | – | tanah |

| PIN31 | B13_L3_P | AA13 | 3.3V | PIN32 | B13_L6_P | W14 | 3.3V |

| PIN33 | B13_L3_N | AB13 | 3.3V | PIN34 | B13_L6_N | Y14 | 3.3V |

| PIN35 | B34_L23_P | Y8 | 1.5V | PIN36 | B34_L20_P | AB7 | 1.5V |

| PIN37 | B34_L23_N | Y7 | 1.5V | PIN38 | B34_L20_N | AB6 | 1.5V |

| PIN39 | GND | – | tanah | PIN40 | GND | – | tanah |

| PIN41 | B34_L18_N | AA6 | 1.5V | PIN42 | B34_L21_N | V8 | 1.5V |

| PIN43 | B34_L18_P | Y6 | 1.5V | PIN44 | B34_L21_P | V9 | 1.5V |

| PIN45 | B34_L19_P | V7 | 1.5V | PIN46 | B34_L22_P | AA8 | 1.5V |

| PIN47 | B34_L19_N | W7 | 1.5V | PIN48 | B34_L22_N | AB8 | 1.5V |

| PIN49 | GND | – | tanah | PIN50 | GND | – | tanah |

| PIN51 | XADC_VN | M9 | Analog | PIN52 | NC | ||

| PIN53 | XADC_VP | L10 | Analog | PIN54 | B34_L25 | U7 | 1.5V |

| PIN55 | NC | – | NC | PIN56 | B34_L24_P | W9 | 1.5V |

| PIN57 | NC | – | NC | PIN58 | B34_L24_N | Y9 | 1.5V |

| PIN59 | GND | – | tanah | PIN60 | GND | – | tanah |

| PIN61 | B16_L1_N | F14 | 3.3V | PIN62 | NC | – | NC |

| PIN63 | B16_L1_P | F13 | 3.3V | PIN64 | NC | – | NC |

| PIN65 | B16_L4_N | E14 | 3.3V | PIN66 | NC | – | NC |

| PIN67 | B16_L4_P | E13 | 3.3V | PIN68 | NC | – | NC |

| PIN69 | GND | – | tanah | PIN70 | GND | – | tanah |

| PIN71 | B16_L6_N | D15 | 3.3V | PIN72 | NC | – | NC |

| PIN73 | B16_L6_P | D14 | 3.3V | PIN74 | NC | – | NC |

| PIN75 | B16_L8_P | C13 | 3.3V | PIN76 | NC | – | NC |

| PIN77 | B16_L8_N | B13 | 3.3V | PIN78 | NC | – | NC |

| PIN79 | NC | – | NC | PIN80 | NC | – | NC |

Rajah 9-1: Penyambung Papan ke Papan CON1 pada Papan Teras

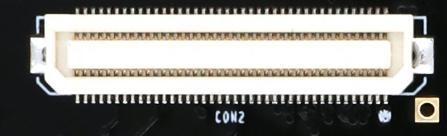

Penyambung Papan ke Papan CON2

Pengepala sambungan wanita 80-pin CON2 digunakan untuk memanjangkan IO biasa BANK13 dan BANK14 FPGA. voltagPiawaian kedua-dua BANK ialah 3.3V.

Penyerahan Pin Papan kepada Penyambung Papan CON2

| CON2 PIN |

bersih Nama |

FPGA PIN |

Voltage Tahap |

CON2 PIN |

bersih Nama |

FPGA PIN |

Voltage Tahap |

| PIN1 | B13_L16_P | W15 | 3.3V | PIN2 | B14_L16_P | V17 | 3.3V |

| PIN3 | B13_L16_N | W16 | 3.3V | PIN4 | B14_L16_N | W17 | 3.3V |

| PIN5 | B13_L15_P | T14 | 3.3V | PIN6 | B13_L14_P | U15 | 3.3V |

| PIN7 | B13_L15_N | T15 | 3.3V | PIN8 | B13_L14_N | V15 | 3.3V |

| PIN9 | GND | – | tanah | PIN10 | GND | – | tanah |

| PIN11 | B13_L13_P | V13 | 3.3V | PIN12 | B14_L10_P | AB21 | 3.3V |

| PIN13 | B13_L13_N | V14 | 3.3V | PIN14 | B14_L10_N | AB22 | 3.3V |

| PIN15 | B13_L12_P | W11 | 3.3V | PIN16 | B14_L8_N | AA21 | 3.3V |

| PIN17 | B13_L12_N | W12 | 3.3V | PIN18 | B14_L8_P | AA20 | 3.3V |

| PIN19 | GND | – | tanah | PIN20 | GND | – | tanah |

| PIN21 | B13_L11_P | Y11 | 3.3V | PIN22 | B14_L15_N | AB20 | 3.3V |

| PIN23 | B13_L11_N | Y12 | 3.3V | PIN24 | B14_L15_P | AA19 | 3.3V |

| PIN25 | B13_L10_P | V10 | 3.3V | PIN26 | B14_L17_P | AA18 | 3.3V |

| PIN27 | B13_L10_N | W10 | 3.3V | PIN28 | B14_L17_N | AB18 | 3.3V |

| PIN29 | GND | – | tanah | PIN30 | GND | – | tanah |

| PIN31 | B13_L9_N | AA11 | 3.3V | PIN32 | B14_L6_N | T20 | 3.3V |

| PIN33 | B13_L9_P | AA10 | 3.3V | PIN34 | B13_IO0 | Y17 | 3.3V |

| PIN35 | B13_L8_N | AB10 | 3.3V | PIN36 | B14_L7_N | W22 | 3.3V |

| PIN37 | B13_L8_P | AA9 | 3.3V | PIN38 | B14_L7_P | W21 | 3.3V |

| PIN39 | GND | – | tanah | PIN40 | GND | – | tanah |

| PIN41 | B14_L11_N | V20 | 3.3V | PIN42 | B14_L4_P | T21 | 3.3V |

| PIN43 | B14_L11_P | U20 | 3.3V | PIN44 | B14_L4_N | U21 | 3.3V |

| PIN45 | B14_L14_N | V19 | 3.3V | PIN46 | B14_L9_P | Y21 | 3.3V |

| PIN47 | B14_L14_P | V18 | 3.3V | PIN48 | B14_L9_N | Y22 | 3.3V |

| PIN49 | GND | – | tanah | PIN50 | GND | – | tanah |

| PIN51 | B14_L5_N | R19 | 3.3V | PIN52 | B14_L12_N | W20 | 3.3V |

| PIN53 | B14_L5_P | P19 | 3.3V | PIN54 | B14_L12_P | W19 | 3.3V |

| PIN55 | B14_L18_N | U18 | 3.3V | PIN56 | B14_L13_N | Y19 | 3.3V |

| PIN57 | B14_L18_P | U17 | 3.3V | PIN58 | B14_L13_P | Y18 | 3.3V |

| PIN59 | GND | – | tanah | PIN60 | GND | – | tanah |

| PIN61 | B13_L17_P | T16 | 3.3V | PIN62 | B14_L3_N | V22 | 3.3V |

| PIN63 | B13_L17_N | U16 | 3.3V | PIN64 | B14_L3_P | U22 | 3.3V |

| PIN65 | B14_L21_N | P17 | 3.3V | PIN66 | B14_L20_N | T18 | 3.3V |

| PIN67 | B14_L21_P | N17 | 3.3V | PIN68 | B14_L20_P | R18 | 3.3V |

| PIN69 | GND | – | tanah | PIN70 | GND | – | tanah |

| PIN71 | B14_L22_P | P15 | 3.3V | PIN72 | B14_L19_N | R14 | 3.3V |

| PIN73 | B14_L22_N | R16 | 3.3V | PIN74 | B14_L19_P | P14 | 3.3V |

| PIN75 | B14_L24_N | R17 | 3.3V | PIN76 | B14_L23_P | N13 | 3.3V |

| PIN77 | B14_L24_P | P16 | 3.3V | PIN78 | B14_L23_N | N14 | 3.3V |

| PIN79 | B14_IO0 | P20 | 3.3V | PIN80 | B14_IO25 | N15 | 3.3V |

Rajah 9-2: Penyambung Papan ke Papan CON2 pada Papan Teras

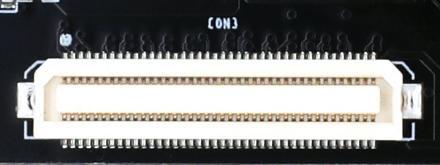

Penyambung Papan ke Papan CON3

Penyambung 80-pin CON3 digunakan untuk memanjangkan IO biasa BANK15 dan BANK16 FPGA. Di samping itu, empat JTAG isyarat juga disambungkan ke papan pembawa melalui penyambung CON3. voltagpiawaian BANK15 dan BANK16 boleh dilaraskan dengan cip LDO. LDO yang dipasang secara lalai ialah 3.3V. Jika anda ingin mengeluarkan tahap standard lain, anda boleh menggantikannya dengan LDO yang sesuai.

Penyerahan Pin Papan kepada Penyambung Papan CON3

| CON3 PIN |

bersih Nama |

FPGA PIN |

Voltage Tahap |

CON3 PIN |

bersih Nama |

FPGA PIN |

Voltage Tahap |

| PIN1 | B15_IO0 | J16 | 3.3V | PIN2 | B15_IO25 | M17 | 3.3V |

| PIN3 | B16_IO0 | F15 | 3.3V | PIN4 | B16_IO25 | F21 | 3.3V |

| PIN5 | B15_L4_P | G17 | 3.3V | PIN6 | B16_L21_N | A21 | 3.3V |

| PIN7 | B15_L4_N | G18 | 3.3V | PIN8 | B16_L21_P | B21 | 3.3V |

| PIN9 | GND | – | tanah | PIN10 | GND | – | tanah |

| PIN11 | B15_L2_P | G15 | 3.3V | PIN12 | B16_L23_P | E21 | 3.3V |

| PIN13 | B15_L2_N | G16 | 3.3V | PIN14 | B16_L23_N | D21 | 3.3V |

| PIN15 | B15_L12_P | J19 | 3.3V | PIN16 | B16_L22_P | E22 | 3.3V |

| PIN17 | B15_L12_N | H19 | 3.3V | PIN18 | B16_L22_N | D22 | 3.3V |

| PIN19 | GND | – | tanah | PIN20 | GND | – | tanah |

| PIN21 | B15_L11_P | J20 | 3.3V | PIN22 | B16_L24_P | G21 | 3.3V |

| PIN23 | B15_L11_N | J21 | 3.3V | PIN24 | B16_L24_N | G22 | 3.3V |

| PIN25 | B15_L1_N | G13 | 3.3V | PIN26 | B15_L8_N | G20 | 3.3V |

| PIN27 | B15_L1_P | H13 | 3.3V | PIN28 | B15_L8_P | H20 | 3.3V |

| PIN29 | GND | – | tanah | PIN30 | GND | – | tanah |

| PIN31 | B15_L5_P | J15 | 3.3V | PIN32 | B15_L7_N | H22 | 3.3V |

| PIN33 | B15_L5_N | H15 | 3.3V | PIN34 | B15_L7_P | J22 | 3.3V |

| PIN35 | B15_L3_N | H14 | 3.3V | PIN36 | B15_L9_P | K21 | 3.3V |

| PIN37 | B15_L3_P | J14 | 3.3V | PIN38 | B15_L9_N | K22 | 3.3V |

| PIN39 | GND | – | tanah | PIN40 | GND | – | tanah |

| PIN41 | B15_L19_P | K13 | 3.3V | PIN42 | B15_L15_N | M22 | 3.3V |

| PIN43 | B15_L19_N | K14 | 3.3V | PIN44 | B15_L15_P | N22 | 3.3V |

| PIN45 | B15_L20_P | M13 | 3.3V | PIN46 | B15_L6_N | H18 | 3.3V |

| PIN47 | B15_L20_N | L13 | 3.3V | PIN48 | B15_L6_P | H17 | 3.3V |

| PIN49 | GND | – | tanah | PIN50 | GND | – | tanah |

| PIN51 | B15_L14_P | L19 | 3.3V | PIN52 | B15_L13_N | K19 | 3.3V |

| PIN53 | B15_L14_N | L20 | 3.3V | PIN54 | B15_L13_P | K18 | 3.3V |

| PIN55 | B15_L21_P | K17 | 3.3V | PIN56 | B15_L10_P | M21 | 3.3V |

| PIN57 | B15_L21_N | J17 | 3.3V | PIN58 | B15_L10_N | L21 | 3.3V |

| PIN59 | GND | – | tanah | PIN60 | GND | – | tanah |

| PIN61 | B15_L23_P | L16 | 3.3V | PIN62 | B15_L18_P | N20 | 3.3V |

| PIN63 | B15_L23_N | K16 | 3.3V | PIN64 | B15_L18_N | M20 | 3.3V |

| PIN65 | B15_L22_P | L14 | 3.3V | PIN66 | B15_L17_N | N19 | 3.3V |

| PIN67 | B15_L22_N | L15 | 3.3V | PIN68 | B15_L17_P | N18 | 3.3V |

| PIN69 | GND | – | tanah | PIN70 | GND | – | tanah |

| PIN71 | B15_L24_P | M15 | 3.3V | PIN72 | B15_L16_P | M18 | 3.3V |

| PIN73 | B15_L24_N | M16 | 3.3V | PIN74 | B15_L16_N | L18 | 3.3V |

| PIN75 | NC | – | PIN76 | NC | – | ||

| PIN77 | FPGA_TCK | V12 | 3.3V | PIN78 | FPGA_TDI | R13 | 3.3V |

| PIN79 | FPGA_TDO | U13 | 3.3V | PIN80 | FPGA_TMS | T13 | 3.3V |

Rajah 9-3: Penyambung Papan ke Papan CON3 pada Papan Teras

Penyambung Papan ke Papan CON4

Penyambung 80-Pin CON4 digunakan untuk memanjangkan data kelajuan tinggi IO dan GTP biasa dan isyarat jam FPGA BANK16. voltagstandard port IO BANK16 boleh dilaraskan oleh cip LDO. LDO yang dipasang secara lalai ialah 3.3V. Jika pengguna ingin mengeluarkan tahap standard lain, ia boleh digantikan dengan LDO yang sesuai. Data berkelajuan tinggi dan isyarat jam GTP dihalakan secara ketat pada papan teras. Talian data adalah sama panjang dan disimpan pada selang waktu tertentu untuk mengelakkan gangguan isyarat.

Penyerahan Pin Papan kepada Penyambung Papan CON4

| CON4 PIN |

bersih Nama |

FPGA PIN |

Voltage Tahap |

CON4 PIN |

bersih Nama |

FPGA PIN |

Voltage Tahap |

| PIN1 | NC | – | – | PIN2 | – | – | |

| PIN3 | NC | – | – | PIN4 | – | – | |

| PIN5 | NC | – | – | PIN6 | – | – | |

| PIN7 | NC | – | – | PIN8 | – | – | |

| PIN9 | GND | – | tanah | PIN10 | GND | – | tanah |

| PIN11 | NC | – | – | PIN12 | MGT_TX2_P | B6 | Perbezaan |

| PIN13 | NC | – | – | PIN14 | MGT_TX2_N | A6 | Perbezaan |

| PIN15 | GND | – | tanah | PIN16 | GND | – | tanah |

| PIN17 | MGT_TX3_P | D7 | Perbezaan | PIN18 | MGT_RX2_P | B10 | Perbezaan |

| PIN19 | MGT_TX3_N | C7 | Perbezaan | PIN20 | MGT_RX2_N | A10 | Perbezaan |

| PIN21 | GND | – | tanah | PIN22 | GND | – | tanah |

| PIN23 | MGT_RX3_P | D9 | Perbezaan | PIN24 | MGT_TX0_P | B4 | Perbezaan |

| PIN25 | MGT_RX3_N | C9 | Perbezaan | PIN26 | MGT_TX0_N | A4 | Perbezaan |

| PIN27 | GND | – | tanah | PIN28 | GND | – | tanah |

| PIN29 | MGT_TX1_P | D5 | Perbezaan | PIN30 | MGT_RX0_P | B8 | Perbezaan |

| PIN31 | MGT_TX1_N | C5 | Perbezaan | PIN32 | MGT_RX0_N | A8 | Perbezaan |

| PIN33 | GND | – | tanah | PIN34 | GND | – | tanah |

| PIN35 | MGT_RX1_P | D11 | Perbezaan | PIN36 | MGT_CLK1_P | F10 | Perbezaan |

| PIN37 | MGT_RX1_N | C11 | Perbezaan | PIN38 | MGT_CLK1_N | E10 | Perbezaan |

| PIN39 | GND | – | tanah | PIN40 | GND | – | tanah |

| PIN41 | B16_L5_P | E16 | 3.3V | PIN42 | B16_L2_P | F16 | 3.3V |

| PIN43 | B16_L5_N | D16 | 3.3V | PIN44 | B16_L2_N | E17 | 3.3V |

| PIN45 | B16_L7_P | B15 | 3.3V | PIN46 | B16_L3_P | C14 | 3.3V |

| PIN47 | B16_L7_N | B16 | 3.3V | PIN48 | B16_L3_N | C15 | 3.3V |

| PIN49 | GND | – | tanah | PIN50 | GND | – | tanah |

| PIN51 | B16_L9_P | A15 | 3.3V | PIN52 | B16_L10_P | A13 | 3.3V |

| PIN53 | B16_L9_N | A16 | 3.3V | PIN54 | B16_L10_N | A14 | 3.3V |

| PIN55 | B16_L11_P | B17 | 3.3V | PIN56 | B16_L12_P | D17 | 3.3V |

| PIN57 | B16_L11_N | B18 | 3.3V | PIN58 | B16_L12_N | C17 | 3.3V |

| PIN59 | GND | – | tanah | PIN60 | GND | – | tanah |

| PIN61 | B16_L13_P | C18 | 3.3V | PIN62 | B16_L14_P | E19 | 3.3V |

| PIN63 | B16_L13_N | C19 | 3.3V | PIN64 | B16_L14_N | D19 | 3.3V |

| PIN65 | B16_L15_P | F18 | 3.3V | PIN66 | B16_L16_P | B20 | 3.3V |

| PIN67 | B16_L15_N | E18 | 3.3V | PIN68 | B16_L16_N | A20 | 3.3V |

| PIN69 | GND | – | tanah | PIN70 | GND | – | tanah |

| PIN71 | B16_L17_P | A18 | 3.3V | PIN72 | B16_L18_P | F19 | 3.3V |

| PIN73 | B16_L17_N | A19 | 3.3V | PIN74 | B16_L18_N | F20 | 3.3V |

| PIN75 | B16_L19_P | D20 | 3.3V | PIN76 | B16_L20_P | C22 | 3.3V |

| PIN77 | B16_L19_N | C20 | 3.3V | PIN78 | B16_L20_N | B22 | 3.3V |

| PIN79 | NC | – | PIN80 | NC | – |

Rajah 9-4: Penyambung Papan ke Papan CON4 pada Papan Teras

Bahagian 10: Bekalan Kuasa

Papan teras AC7A200 FPGA dikuasakan oleh DC5V melalui papan pembawa, dan ia dikuasakan oleh antara muka Mini USB apabila ia digunakan secara bersendirian. Sila berhati-hati untuk tidak membekalkan kuasa oleh Mini USB dan papan pembawa pada masa yang sama untuk mengelakkan kerosakan. Gambar rajah reka bentuk bekalan kuasa pada papan ditunjukkan dalam Rajah 10-1.

Rajah 10-1:Bekalan Kuasa pada skema papan teras

Papan teras dikuasakan oleh +5V dan ditukar kepada +3.3V, +1.5V, +1.8V, +1.0V bekalan kuasa empat hala melalui tiga cip bekalan kuasa DC/DC TLV62130RGT. Arus +1.0V boleh sehingga 6A, dan tiga arus keluaran yang lain boleh sehingga 3A. VCCIO dijana oleh satu LDOSPX3819M5-3-3. VCCIO terutamanya membekalkan kuasa kepada BANK15 dan BANK16 FPGA. Pengguna boleh menukar IO BANK15,16 kepada vol yang berbezatage standard dengan menggantikan cip LDO mereka. 1.5V menjana VTT dan VREF voltages diperlukan oleh DDR3 melalui TPS51200 TI. Bekalan kuasa 1.8V MGTAVTT dan MGTAVCC untuk transceiver GTP dijana oleh cip TPS74801 TI. Fungsi setiap pengagihan kuasa ditunjukkan dalam jadual berikut:

| Bekalan Kuasa | Fungsi |

| +1.0V | Vol. Teras FPGAtage |

| +1.8V | FPGA tambahan voltage, bekalan kuasa TPS74801 |

| +3.3V | VCCIO of Bank0, Bank13 dan Bank14 of FPGA, QSIP FLASH, Clock Crystal |

| +1.5V | DDR3, Bank34 dan Bank35 FPGA |

| VREF,VTT(+0.75V) | DDR3 |

| CCIP(+3.3V) | FPGA Bank15, Bank16 |

| MGTAVTT(+1.2V) | GTP Transceiver Bank216 FPGA |

| MGTVCC(+1.0V) | GTP Transceiver Bank216 FPGA |

Oleh kerana bekalan kuasa Artix-7 FPGA mempunyai keperluan jujukan kuasa hidup, dalam reka bentuk litar, kami telah mereka bentuk mengikut keperluan kuasa cip, dan kuasa hidup ialah 1.0V->1.8V->(1.5 V, 3.3V, VCCIO) dan 1.0V-> MGTAVCC -> MGTAVTT, reka bentuk litar untuk memastikan operasi normal cip.

Litar kuasa pada papan teras FPGA AC7A200 ditunjukkan dalam Rajah 10-2:

Rajah 10-2: Bekalan Kuasa pada Papan Teras FPGA AC7A200

Bahagian 11: Dimensi Saiz

Rajah 11-1: Papan Teras FPGA AC7A200 (Atas View)

Rajah 11-2: Papan Teras FPGA AC7A200 (Bawah View)

Dokumen / Sumber

|

Papan Pembangunan FPGA ALINX AC7A200 ARTIX-7 [pdf] Manual Pengguna AC7A200 ARTIX-7 FPGA Development Board, AC7A200, ARTIX-7 FPGA Development Board, FPGA Development Board, Development Board, Board |